干货分享|同步整流芯片误关断致产品效率明显降低分析

1 背景

同步整流作为目前开关电源输出端整流常用的电路,具有提升效率、减小产品体积等明显优势。在对某机壳系列产品进行国产同步整流IC 的产品改良中发现:将同步整流IC 替换原IC 后,样机启机后效率只有77%,相较于原样机83% 的规格值降低6%。本文将针对此问题进行分析和解决,并分享一些关于同步整流芯片参数适配的经验。

2 问题描述

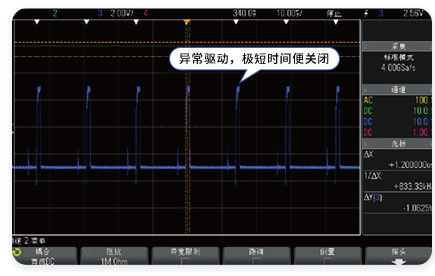

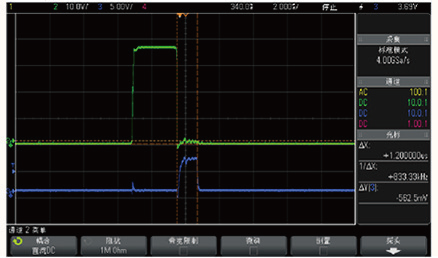

在更换同步整流控制IC 后启机效率明显降低,首先从同步整流工作异常开始着手测量。如图1 所示,在同步整流驱动波形测量的同时用热成像仪测量同步整流MO 管的温度,结果显示器件在常温下工作一分钟左右温度已经高达130℃,明显异常。

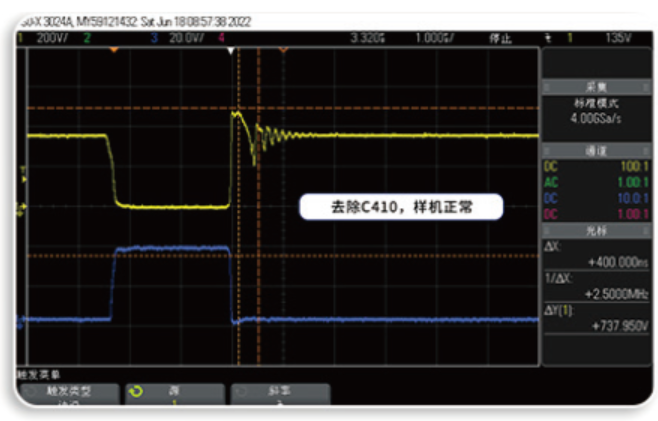

图1 同步整流驱动波型测量异常图

从图1 可以看出,同步整流驱动信号在导通后极短的时间内关闭,且每个周期都如此。对比图2 的理想状态后可以判断产品同步整流异常关断,输出电流通过MOS管体二极管导通,最终导致效率明显下降且器件温度超高。

图2 同步整流驱动波型测量理想图

3 问题分析

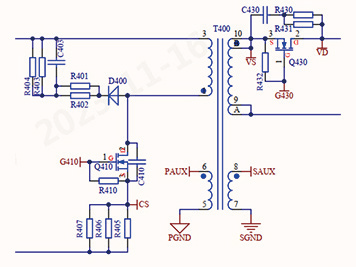

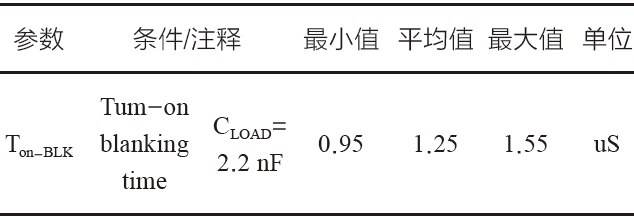

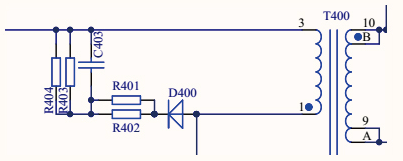

该系列产品功率拓扑为反激和同步整流(图3),同步整流电路工作原理较为简单,即IC 通过检测同步整流MOS 管源漏级电压,当反激原边MOS 管开通时,IC 检测到源级电压低于漏级电压,同步整流MOS 管关断;当反激原边MOS管关断时,电感电压感应电压反向,IC 检测到源级电压高于漏级电压,给出驱动信号同步整流MOS 管正向导通。根据图1 测试的波形可以看出,同步整流MOS 管开通1.2uS 后便关断,这与IC 的规格书和实际测量值中的空白导通时间(1.25us)相吻合。

图3

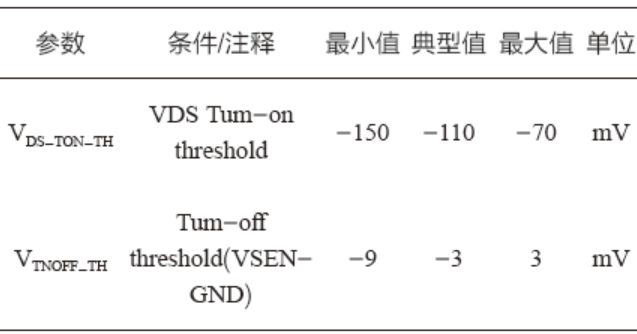

测量显示其在最小导通时间过后就关闭驱动,由此判断是触发了同步整流MOS 的关断条件。(这里同时测量SR 采样脚波形以及驱动波)

从测量结果可以发现,在空白导通时间内,SR 采样脚(图4 中绿色波形)处电压始终在振荡,在1.2 us结束时,依然有高频的振荡波峰幅值。在查询规格书后得知,采样脚在小于3 mV 时会迫使芯片驱动关闭。

图4

从测量结果可以发现,在空白导通时间内,SR 采样脚(图4 中绿色波形)处电压始终在振荡,在1.2 us结束时,依然有高频的振荡波峰幅值。在查询规格书后得知,采样脚在小于3 mV 时会迫使芯片驱动关闭。

故问题点可以确认为——有某处的干扰导致SR 采样异常。

由反激原理可知,副边开通时对应原边MOS关断,而原边关断时变压器漏感、层间电容及主MOS 结电容会产生高频尖峰振荡,该振荡依然会通过变压器耦合到副边,导致副边MOS 管的源级电压震荡,影响同步整理的采样电压,导致MOS 管提前关断。

图5

4 解决措施及验证结果

4.1 整改方向一:源头出发,削减振荡。

方案①:减小变压器漏感,从根本上减小能量振荡。原边振荡的能量来源为未能传输到副边的漏感能量,减小漏感可以直观地减弱振荡幅值,从而改善副边的采样环境。(此种方案受限于变压器设计及制作工艺,实测时所用变压器原边为265 uH 电感,5.6 uH 漏感,此类仅2.1% 漏感变压器继续优化较困难)

方案②:减小振荡的电容容值

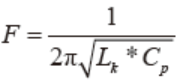

主MOS 关断时的原边振荡为变压器漏感、层间电容及主MOS 结电容的振荡。查看原理图可知,其设计上额外在MOS 的DS 间添加并联电容C410。由振荡频率公式 (LK为变压器漏感,Cp为等效电容,Cp=C410 + MOS 结电容)可知:减小C410,即减小Cp可以提高振荡频率,在同样阻尼衰减的作用下,高频率的振荡能够在更快的时间内达到平稳,也就是可以抢在副边SR 采样消隐时间内,把振荡幅值以及对副边的影响降到最低。

(LK为变压器漏感,Cp为等效电容,Cp=C410 + MOS 结电容)可知:减小C410,即减小Cp可以提高振荡频率,在同样阻尼衰减的作用下,高频率的振荡能够在更快的时间内达到平稳,也就是可以抢在副边SR 采样消隐时间内,把振荡幅值以及对副边的影响降到最低。

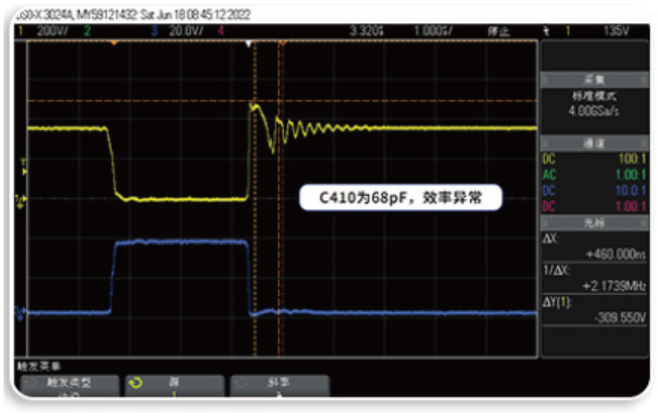

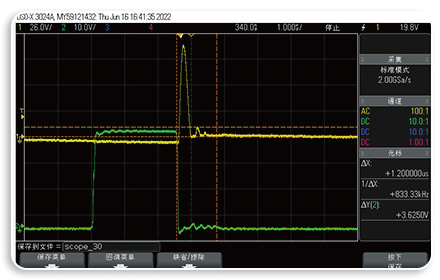

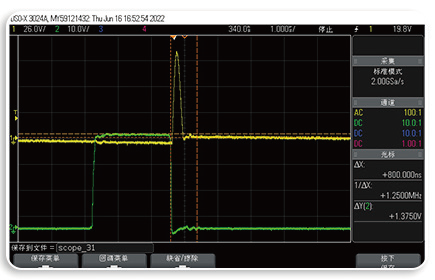

下图6 和图7 为实测波形。主MOS 应力波形(黄)和副边SR 采样波形(蓝)。

图6

在有C410 电容时,第一个波周期为440 ns(频率2.17 MHz),第二个波周期为220 ns(频率4.54 MHz)在去除C410 电容,第一个波周期为400 ns(频率2.5 MHz),第二个波周期为180ns(频率5.5 MHz)如图7 所示,去除C410 电容的振荡波形平稳速度更快,有利于提高副边SR 的采样精确度。

图7

4.2 整改方向二:改善RCD吸收参数,削减振荡

方案①:减小吸收电容

吸收电容串联二极管的寄生电容与漏感在正常工作中也存在振荡,可以通过减小吸收电容可以改善这一点。实操中,将原有的222 吸收电容更变为102 电容,也可以达到改善采样信号的目的。但是吸收电容的减小导致主MOS 应力尖峰的明显增大,已超过承受规格,故该方案在此型号中不可取。

图8

方案②:增大吸收电阻

吸收电组的增大,可以使得每个周期内通过RCD泻放的漏感能量减少,即吸收电容与漏感的谐振能量减少,从而改善对副边SR 采样。

从以下图9 和图10 波形可以看到,在吸收电阻从75 K 增大到100 K 时,二次振铃的幅值由3.6 V 降低至1.375 V。

图9

图10

最后针对空白导通时间后采样扰动导致SR 芯片误关断问题作出改善措施汇总如下:

①减小变压器漏感;②减小振荡的电容容值(主mos 结电容及并联电容);③减小原边吸收电容;④增大原边吸收电阻;⑤ SR 采样走线,单点走线至驱动MOS 对应引脚。

结合上述优化方案,我们在产品设计时首先对于变压器设计很关键,对于反激变压器来说,可以尽量通过绕法设计去减小变压器漏感,再平衡产品效率以及EMC 性能的情况下尽量减小主mos 结电容及并联电容容值;最后,再PCB 布局以及走线时对于SR 这类易受干扰的走线,需单点连接至驱动MOS 对应引脚。同时改善结果判定方法:保证SR 采样信号的平稳度,波形达到平稳的时间小于SR 芯片最小导通时间,最终导入措施后产品的效率也恢复正常与替换前一致如图11 所测试到波形。

不同的IC 对于同步整流MOS 管的开通以及关断的检测条件都有不同,希望通过本案例的调试与分析后得出一些对同步整流误关断导致效率降低问题的解决方案,可以为后续类似的问题提供一些经验与帮助。

(本文来源于EEPW 2023年12月期)

评论