D型触发器的电路和操作

D型触发器是基本的数字存储器元件。在这里,我们检查它们的输入输出行为和内部电路。

本文引用地址://m.amcfsurvey.com/article/202404/457625.htm逻辑门是所有数字技术的组成部分。然而,只有组合逻辑电路是不可能实现现代世界庞大的计算功能的。在完全由组合逻辑组成的电路中,输出仅取决于输入的当前状态。所有信号通过互连的逻辑门直接从输入移动到输出。

为了实现我们与当今数字技术相关的先进计算和信号处理,我们需要组合逻辑和数字存储器。换句话说,我们需要时序逻辑。虽然组合逻辑允许我们构建有用的设备,如加法器、多路复用器和编码器,但正是时序逻辑让我们进入微处理器领域。

在时序逻辑电路中,输出取决于输入信号的序列——包括当前状态和历史。这允许创建具有存储器的数字设备,例如锁存器和触发器。然而,尽管这两种电路类型都起到数字存储设备的作用,但它们之间有一个重要的区别:

锁存器是电平触发的,这意味着当“使能”输入处于活动状态时(例如,在时钟信号的逻辑高脉冲期间),它会对输入信号做出响应。

触发器是边缘触发的,这意味着当“使能”输入改变状态时,它对输入信号做出响应——例如,在时钟信号的上升沿。

在实际应用中,通常更希望有一个只在特定事件发生时对输入状态敏感的存储设备。因此,触发器的应用要广泛得多。

在我看来,D型触发器是最重要的触发器——我甚至称之为最重要的数字存储器子电路。在这篇文章中,我们将了解它的电学行为和内部结构。

什么是D型触发器?

D型触发器以其单个数据输入而命名,它正是做存储器单元需要做的事情——它在控制信号的有效转换时刻将输入逻辑电平存储为输出电压,而在所有其他时间只保留输出电压。

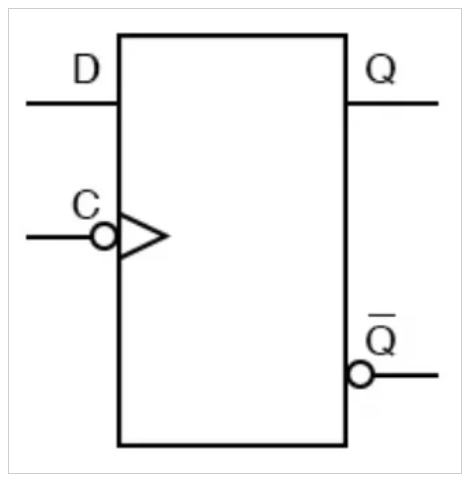

图1显示了一个基本的D型触发器。如您所见,它有四个终端:

数据输入(D)。

时钟或控制输入(C)。

一个输出(Q)。

输出的反相版本(Q̅)。

基本D型触发器的电路符号。

图1。基本D型触发器的电路符号。端子是数据输入端(D)、时钟或控制输入端(C)、输出端(Q)和输出端的反相版本(Q̅)。图片由Tony R.Kuphaldt提供

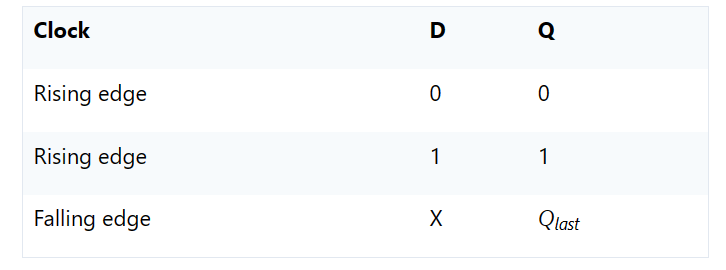

表1描述了响应时钟信号的上升沿的D型触发器的操作。

表1。D型触发器的真值表。

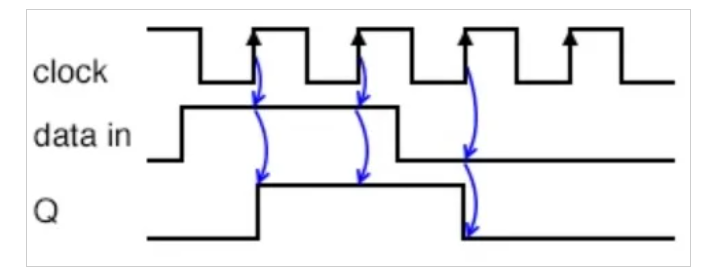

下降沿行中的X表示D的逻辑电平无关。Q仅受上升沿处的输入状态的影响。在时钟信号的上升沿,对数据输入进行采样并将其传递到Q输出。通过查看图2中的时序图,我们可以在时域中看到这一点。

D型触发器的时序图。

图2:D型触发器的时序图。图片(经修改)由Tony R.Kuphaldt提供

由同一时钟信号的上升沿或下降沿控制的八个D型触发器可以用作一字节(8位)寄存器。当与解码电路相结合时,一个字节寄存器的集合起到存储器组的作用。

为了理解D型触发器的内部逻辑门结构,让我们检查以下功能块:

D锁存器。

脉冲检测器。

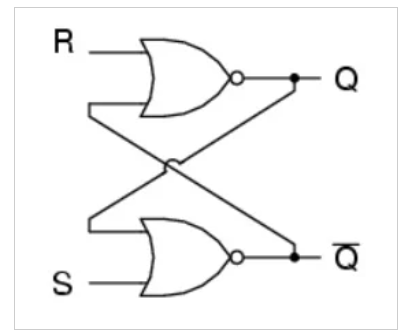

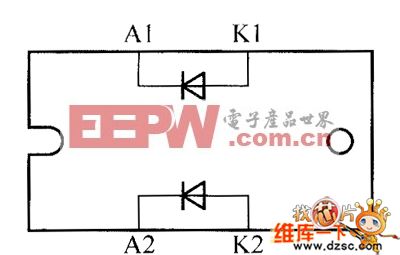

置位-复位(S-R)锁存器是时序逻辑的基础子电路。这种通过反馈实现存储器的锁存器可以由NOR门或NAND门构建。图3显示了实现为两个交叉耦合NOR门的S-R锁存器。

使用两个NOR门实现的S-R锁存器。

图3。S-R锁存器实现为两个交叉耦合的NOR门。图片由Tony R.Kuphaldt提供

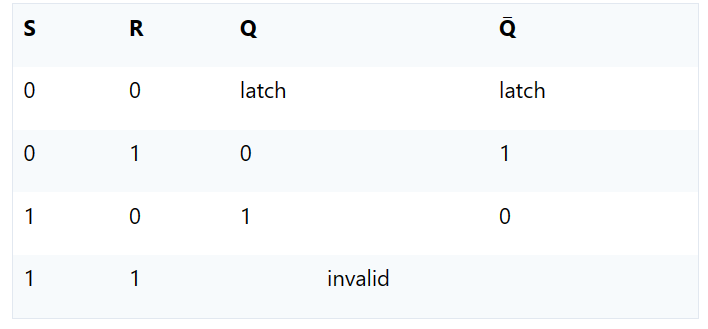

将输出信号反馈到输入端子允许S-R锁存器保持先前的输出状态。下面的真值表指定了锁存器的输入输出行为。

表2。S-R锁存真值表。

要理解这种行为,请考虑以下事件序列:

首先,假设s为高,R为低。因此Q将是高的。

现在将S驱动至逻辑低。两个输入现在都是低电平,而Q仍然是高电平——它被“锁存”,这意味着它保留了以前的状态。

现在将R驱动至逻辑高电平。在R逻辑为高且S逻辑为低的情况下,Q将为低。

现在将R驱动至逻辑低。再一次,两个输入都是低的,但这次Q是低的。

相同的输入组合在步骤4中产生与在步骤2中不同的输出状态。这是因为电路同时受到当前输入状态和先前输出状态的影响。

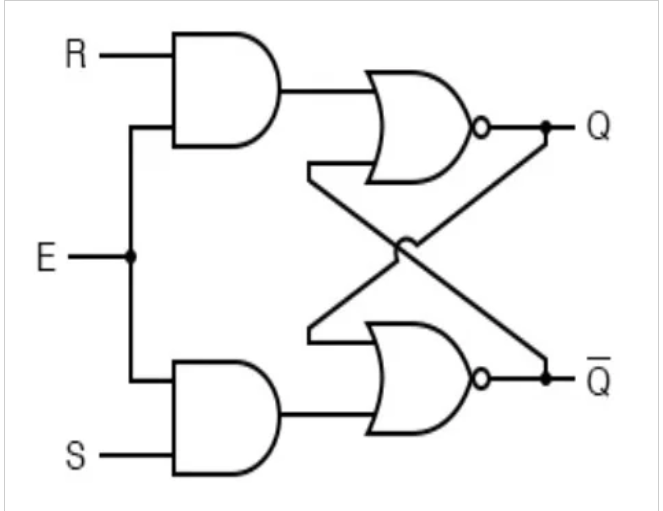

为了使S-R锁存器更有用,我们需要额外的电路,使我们能够确定锁存器何时会或不会对其输入状态做出响应。图4显示了一个“门控”S-R锁存器,即具有启用/禁用信号的S-R锁闩器。控制信号标记为E,表示“启用”

门控S-R锁存器。

图4。门控S-R锁存器。图片由Tony R.Kuphaldt提供

有了这个附加,我们现在有了一个电平触发的锁存器——当E为低时,锁存器的作用就好像S和R为低一样。换言之,E上的逻辑低将锁存器置于其保持先前输出模式,而与S和R输入的真实状态无关。

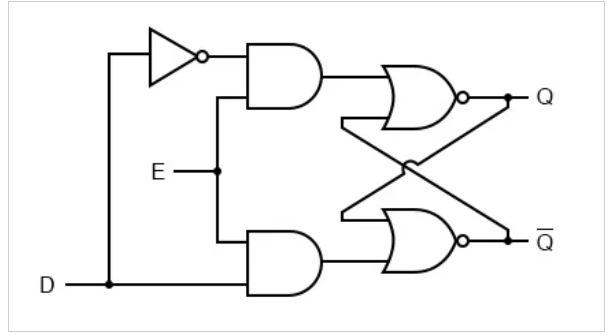

从技术上讲,我们不需要同时使用设置和重置输入来存储单个内存。简单地存储一个输入信号的逻辑电平的存储器单元具有更直观的意义。这就是为什么我们有D锁存器(图5)。

一个D锁存器。

图5。一个D锁存器。图片由Tony R.Kuphaldt提供

如图所示,D锁存器简单地是门控S-R锁存器,其中S输入被重命名为D,并且R输入总是D的倒数。这种布置使得S=R=1(无效)状态和S=R=0(锁存器)状态不可能。如表3所示,Q跟随D,并且锁存模式仅通过E信号实现。

表3。D锁存器的真值表。

脉冲检测器

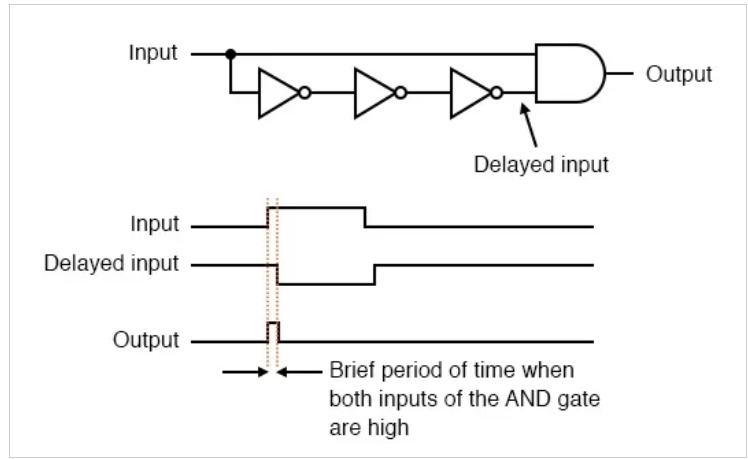

为了将电平触发的D锁存器转换为边缘触发的D型触发器,我们需要一个脉冲检测器——一种将宽脉冲转换为与脉冲的上升沿或下降沿对齐的非常窄的脉冲的电路。图6中的图表描述了一种实现脉冲检测器的方法。这里,多个串联的反相器会产生短延迟。AND门使用主输入和延迟输入来创建窄脉冲。

使用串联的多个逆变器构建的脉冲检测器。

图6。使用串联的多个逆变器构建的脉冲检测器。图片由Tony R.Kuphaldt提供

如果我们在将D锁存器的E信号馈送到AND门之前将其通过脉冲检测器,那么我们将有一个D型触发器,它的作用就好像它只在E信号的上升沿或下降沿时刻对输入做出响应一样。实际上,触发器仍然是电平触发的,但现在感兴趣的电平是脉冲检测器输出的激活状态。这种活跃状态总是非常短暂的。

总结

D型触发器是最先进的数字技术的重要组成部分。在我们结束之前,我应该指出,上面描述的结构并不是创建一个结构的唯一方法。例如,上升沿触发的D型触发器可以由连接在一起的三个S-R锁存器制成。无论哪种方式,电路在设计和操作上都保持相当简单。

评论