高频锁相环的可测性设计

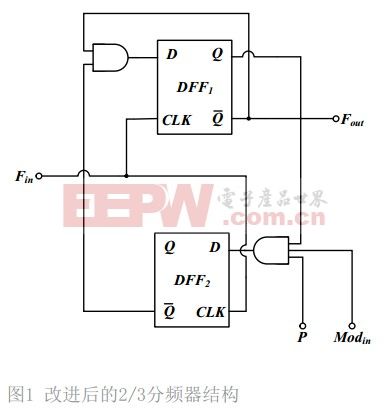

一种简单的测试方法就是将输出频率分频,通过测量分频后的频率fout推算VC O的振荡频率。这种分频器测试方法比较简单,只需要在VCO的输出端增加输出分频器,检测降频后的信号频率,即可由公式:

![]()

推算出VCO的振荡频率。式中N为输出分频器的分频值。

按照分频测试的方法来测试,每次都必须在锁相环 达到稳定的锁定状态时才能测量。GHz高 频锁相环

达到稳定的锁定状态时才能测量。GHz高 频锁相环 的锁定时间一般为微秒量级,于是锁相环

的锁定时间一般为微秒量级,于是锁相环 的频率测量通常需要几毫秒。对于电路 测试来说,这是一个相对较长的时间。更为理想的测试方法是尽量采用简单的硬件资源,在 不影响电路性能的情况下,在较短的测试时间内完成测试。

的频率测量通常需要几毫秒。对于电路 测试来说,这是一个相对较长的时间。更为理想的测试方法是尽量采用简单的硬件资源,在 不影响电路性能的情况下,在较短的测试时间内完成测试。

边界扫描是目前大规模集成电路中常用的测试方法。IEEE1149?1规范了边界扫描方法和指 令。基于集成电路中常见的边界扫描单元电路,本文将介绍一种边界扫描的测试方 案来测试锁相环 。

。

如前所述,要测试的锁相环 采用了环形VCO振荡器,环形VCO的振荡频率与其延时存在如下关系:

采用了环形VCO振荡器,环形VCO的振荡频率与其延时存在如下关系:![]()

其中:Tdelay是环形振荡器的延迟时间;fvco是VCO的振荡频率。采用边界扫描电路测量出VCO模块的延迟Tdelay,进而计算振荡器的工作频率。

VCO的输出频率受控制电压的控制,可通过改变控制电压的大小并检测每个控制电压对应的VCO延迟,利用式(2)计算输出频率,最后得到输出频率范围。

这种方案将闭环电路的频率测量转换成开环电路的延迟测量(通常该延迟为纳秒量级),时间 的节省将非常可观。同时,已经成熟的边界扫描技术,并不会增加太大的设计难度和测试复杂度,对设计者和测试者来说,只需遵照一定的规范完成即可。采用标准的边界扫描单元,硬件的开销也不大。对大规模集成电路中的锁相环电路,采用边界扫描测试方案显然优于前一种分频测试方案。

2.2 锁定时间测试

锁相环的锁定时间是锁相环的重要指标。如何判断锁相环已经达到锁定状态以及锁定时间的计算也是锁相环要测试的内容。

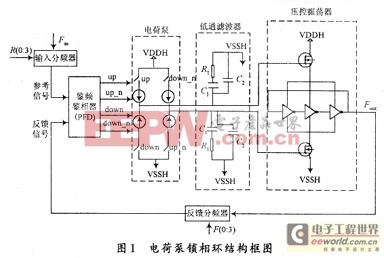

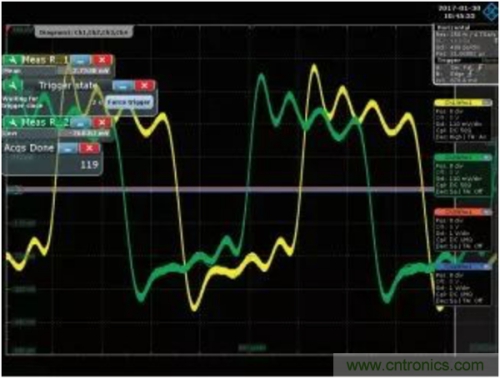

根据锁相环的原理,锁相环的重要功能就是锁定相位。电路锁定时,鉴频鉴相器的2个输入信号:参考信号和反馈信号相差为0,鉴频鉴相器输出无效电平,电荷泵开关处于开启状态,VCO的控制电压保持恒定。因此,参考信号和反馈信号、鉴频鉴相器的输出信号、VCO的控制电压等都可以作为电路锁定的判别依据。本文选取了VCO的控制电压作为判断依据,

3 测试电路实现

3.1 测试电路

电荷放大器相关文章:电荷放大器原理

鉴相器相关文章:鉴相器原理

锁相环相关文章:锁相环原理

锁相放大器相关文章:锁相放大器原理

评论