AD6645型模/数转换器在软件无线电中的应用

1 引言

软件无线电是基于一种通用的硬件平台,通过加载不同的软件实现不同的无线通信功能,它是一种全新的开放式结构体系,其核心设计思想是在尽可能靠近天线的地方使用宽带a/d转换器,在射频段将信号数字化,在dsp中用软件实现所有功能,受硬件发展水平的限制,目前存在二大瓶颈:一是a/d转换器的速率和性能,二是dsp的处理速度。a/d转换器在系统中所处的位置是很关键的,因为它直接反映软件化的程度,对理想的软件无线电而言,a/d转换器的动态范围必须为100db-120db,最大信号输入频率在1ghz-5ghz之间,目前器件发展水平很难实现这些技术指标,即使实现了这些指标,如此大的数据量也是后面的dsp无法承担的,所以折衷的方案就是进行中频采样。

2 选择依据

a/d转换器的选择既要考虑a/d转换器的性能又要考虑能满足系统所要求的动态范围和性能指标。评价a/d转换器的性能指标主要有a/d转换位数、无寄生动态为((sfdr)、信噪比(snr)、转换速率、量化灵敏度等。一般来说a/d转换器的转换位数越多越好,转换位数越多,其动态范围就越高。由于本设计硬件平台中选用的hsp50214型可编程下变频器输入是14位,因此选用14位的a/d转换器。在目前的无线电中频方案里,一般都采用欠采样技术,采样频率一般为几十赫兹至上百赫兹,若对中频为70mhz、带宽为2mhz的信号(am或fm)采用40mhz采样,由a/d转换器的理论snr公式可知:

snr=6.02b+1.76+10log10(fs/2fmax)db =6.02×14+1.76+10log10(40×106/2×71×106)db ≈81db

式中,b为a/d转换器位数,fs为采样速率,fmax为输入信号的最高频率。在实际测试中,a/d转换器的最后2位会不停变化,其有效位(enob)为12位,代入上式后可得snr为69db。所以ad6644和ad6645都能满足要求,由于ad6645的孔径抖动小于0.2ps,ad6645的孔径抖动小于0.3ps,所以在中频接收系统中用ad6645效果会更好一些。目前市场上的高速采样器件种类繁多,表1列出一些主流a/d转换器的主要技术参数。

3 主要特点

ad6645是带宽a/d转换器系列中继ad9042(12位41ms/s)和ad6640(12位65ms/s)、ad6644(14位,40ms/s,65ms/s)后的第四代产品,其主要特点如下:

保持采样率可达80ms/s;

工作带宽达270mhz;

多音无寄生动态范围(sfdr)为100db;

对200mhz信号采样时采样抖动时间为0.1ps;

数字输出可以在3.3v下工作,便于与数字asic接口;

功耗为1.5w。

4 工作原理

如图1所示,ad6645采用3级子区式转换结构,这种设计的好处是保证了转换的精度和速度又实现了较小的功耗和封装尺寸,ad6645有2个互补的模拟输入端ain和ain反,2路输入经过缓冲后先进入第一个保持器th1,encode脉冲为高时th1处于保持状态,th1的保持值作为5位a/d转换器adc1的输入,其输出驱动1个5位d/a转换器dac1。经过延迟后的模拟信号减dac1的输出后在th3的输入端产生第一个剩余信号,保持器th2补偿由adc1造成的延迟。

在由1个5位adc2、5位dac2和1个th4组成的第二转换阶段中,th4保持的第一个剩余信号减去dac2的量化输出产生第二个剩余信号作为th5的输入,th5驱动最后一个6位a/d转换器adc3,将adc1、adc2和adc3的输出相加并经数字误差校正逻辑修正后将得到并行输出的14位二进制补码数据。

5 实际应用

5.1 时钟输入电路

为了保证14位的精度,对ad6645的采样时钟质量要求较高且要具有低相位噪声。为了获得最佳性能,ad6645的时钟必须采用差分输入,时钟信号可通过1个变压器或电容器交流耦合到encode和encode反脚,这2个引脚在片内被偏置,无需外加偏置电路,为了提高时钟信号的差分输入质量,本设计采用了motorola公司的mc100lve16型低压差分接收器,它的抗抖动性能非常好,整个连接电路如图2所示,差分输出端q和q反的电压较小,和后面的ad6645输入电压不匹配,因此分别加上偏置电压。

5.2 模拟输入电路

作为新型的高速、大动态范围a/d转换器,ad6645的模拟信号输入也应为差分形式,因为在模拟信号阶段差分输入对偶次谐波有很高的共模抑制比,可以提高电路的性能,采用差分输入在制作pcb时也有很大的好处:其一是对电源和地引入的噪声有很高的共模抑制比;其二是对由本振反馈引入的共模信号也有很强的抑制作用。

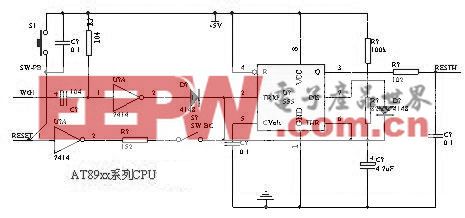

ad6645的模拟输入电压被偏置到2.4v,在电路内部每个模拟输出通过1只500ω电阻器连接到2.4v偏置电压和差分缓冲器,因此驱动ad6645的模拟信号必须通过交流耦合送进输入端,实际使用时可以采用如图3所示的4:1阻抗变换器来实现。

5.3 信号输出

ad6645的数字输出有固定的输出摆动率(1v/ns),制作pcb时,1个cmos门加上布线会产生大约10bf的电容,因此每有1位转换输出就会有10ma的动态电流出入器件,满量程输出即14位输出时就会有140a的电流,所以在每条输出数据线上要串联100ω的电阻器以限制这些电流流入接收器件,在软件无线电的中频采样方案中,采用在ad6645后接1个hsp50214b型下变频器来进行降频、抽取、滤波等一系列处理,二者之间加1个74lcx574型锁存器。数据准备输出信号dry作为74lcx574的时钟输入,并经反相器后作为hsp50214b型数字下变频器的前端时钟clkin输入。

5.4 注意事项

ad6645对时钟电路要求比较苛刻,该电路接收到的任何噪声都会造成数字化性能的恶化和总体性能的降低,因此一定要将其与数字输出和模拟输入隔离开来,除了布线应尽量短外,整个采样电路下面要大面积覆铜接地以降低干扰,模拟部分和数字部分的供电电源avcc(5v)和dvcc(3.3v)要尽量分开,在电源滤波中使用高频特性好的陶瓷电容器来抑制噪声,数字地和模拟地应该分开并通过高频磁珠单点接地。在实际调试时,时钟信号不理想,可用门电路进行整形,dry信号较小,也可用nc7sz32型门电路进行整形驱动。

6 结束语

作为未来通信的发展方向,软件无线电以其灵活性和通用性引起了全世界的关注,而a/d转换和d/a转换部分在软件无线电中起着关键的作用,因此器件的选取及外围电路的设计显得非常重要,尤其是在抗干扰方面要更加注意。ad6645以其优越的性能成为目前软件无线电接收机中a/d转换器的理想选择。

评论