影响开关模式、DC-DC转换器效率的主要因

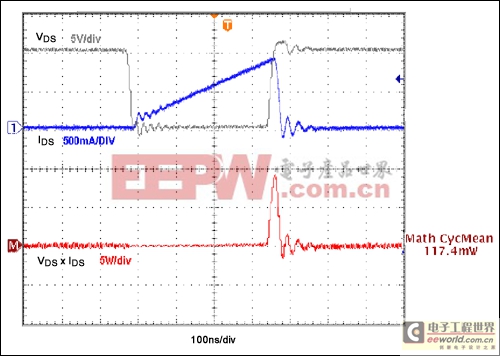

图4. 开关损耗发生在MOSFET通、断期间的过渡过程

开关损耗随着SMPS频率的升高而增大,这一点很容易理解,随着开关频率提高(周期缩短),开关过渡时间所占比例增大,从而增大开关损耗。开关转换过程中,开关时间是占空比的二十分之一对于效率的影响要远远小于开关时间为占空比的十分之一的情况。由于开关损耗和频率有很大的关系,工作在高频时,开关损耗将成为主要的损耗因素。

MOSFET的开关损耗(PSW(MOSFET))可以按照图3所示三角波进行估算,公式如下:

P SW(MOSFET)= 0.5 × V D× I D× (t SW(ON)+ t SW(OFF)) × f S

其中,VD为MOSFET关断期间的漏源电压,ID是MOSFET导通期间的沟道电流,tSW(ON)和tSW(OFF)是导通和关断时间。对于降压电路转换,VIN是MOSFET关断时的电压,导通时的电流为IOUT。

为了验证MOSFET的开关损耗和传导损耗,图5给出了降压转换器中集成高端MOSFET的典型波形:VDS和IDS。电路参数为:VIN= 10V、VOUT= 3.3V、

在图5可以看出,开关变化不是瞬间完成的,电流和电压波形交叠部分导致功率损耗。MOSFET“导通”时(图2),流过电感的电流IDS线性上升,与导通边沿相比,断开时的开关损耗更大。

利用上述近似计算法,MOSFET的平均损耗可以由下式计算:

PT(MOSFET) = P COND(MOSFET)+ P SW(MOSFET)

= [(I 1 3- I 0 3)/3] × R DS(ON)× V OUT/V IN+ 0.5 × V IN× I OUT× (t SW(ON)+ t SW(OFF)) × f S

= [(1 3- 0 3)/3] × 0.1 × 3.3/10 + 0.5 × 10 × 0.5 × (38 × 10 -9) × 1 × 10 6

= 0.011 + 0.095 = 106mW

这一结果与图5下方曲线测量得到的117.4mW接近,注意:这种情况下,fS足够高,PSW(MOSFET)是功耗的主要因素。

图5. 降压转换器高端MOSFET的典型开关周期,输入10V、输出3.3V (输出电流500mA)。开关频率为1MHz,开关转换时间是38ns。

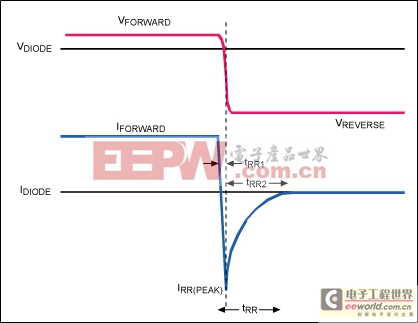

与MOSFET相同,二极管也存在开关损耗。这个损耗很大程度上取决于二极管的反向恢复时间(tRR),二极管开关损耗发生在二极管从正向导通到反向截止的转换过程。

当反向电压加在二级管两端时,正向导通电流在二极管上产生的累积电荷需要释放,产生反向电流尖峰(IRR(PEAK)),极性与正向导通电流相反,从而造成V × I功率损耗,因为反向恢复期内,反向电压和反向电流同时存在于二极管。图6给出了二极管在反向恢复期间的PN结示意图。

图6. 二极管结反偏时,需要释放正向导通期间的累积电荷,产生峰值电流(IRR(PEAK))。

了解了二极管的反向恢复特性,可以由下式估算二极管的开关损耗(PSW(DIODE)):

P SW(DIODE)= 0.5 × V REVERSE× I RR(PEAK)× t RR2× f S

其中,VREVERSE是二极管的反向偏置电压,IRR(PEAK)是反向恢复电流的峰值,tRR2是从反向电流峰值IRR到恢复电流为正的时间。对于降压电路,当MOSFET导通的时候,VIN为MOSFET导通时二极管的反向偏置电压。

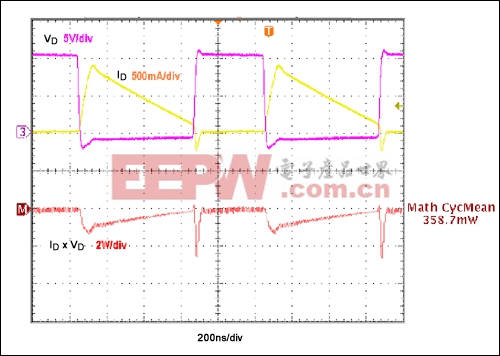

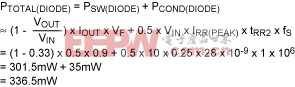

为了验证二极管损耗计算公式,图7显示了典型的降压转换器中PN结的开关波形,VIN= 10V、VOUT= 3.3V,测得IRR(PEAK)= 250mA、IOUT= 500mA、

该结果接近于图7所示测量结果358.7mW。考虑到较大的VF和较长的二极管导通周期,tRR时间非常短,开关损耗(PSW(DIODE))在二极管损耗中占主导地位。

图7. 降压型转换器中PN结开关二极管的开关波形,从10V输入降至3.3V输出,输出电流为500mA。其它参数包括:1MHz的fS,tRR2为28ns,VF= 0.9V。

提高效率

基于上述讨论,通过哪些途径可以降低电源的开关损耗呢?直接途径是:选择低导通电阻RDS(ON)、可快速切换的MOSFET;选择低导通压降VF、可快速恢复的二极管。

直接影响MOSFET导通电阻的因素有几点,通常增加芯片尺寸和漏源极击穿电压(VBR(DSS)),由于增加了器件中的半导体材料,有助于降低导通电阻RDS(ON)。另一方面,较大的MOSFET会增大开关损耗。因此,虽然大尺寸MOSFET降低了RDS(ON),但也导致小器件可以避免的效率问题。

当管芯温度升高时,MOSFET导通电阻会相应增大。必须保持较低的结温,使导通电阻RDS(ON)不会过大。导通电阻

MOSFET的开关损耗与器件电容有关,较大的电容需要较长的充电时间,使开关切换变缓,消耗更多能量。米勒电容通常在MOSFET数据资料中定义为反向传输电容(CRSS)或栅-漏电容(CGD),在开关过程中对切换时间起决定作用。

米勒电容的充电电荷用QGD表示,为了快速切换MOSFET,要求尽可能低的米勒电容。一般来说,MOSFET的电容和芯片尺寸成反比,因此必须折衷考虑开关损耗和传导损耗,同时也要谨慎选择电路的开关频率。

对于二极管,必须降低导通压降,以降低由此产生的损耗。对于小尺寸、额定电压较低的硅二极管,导通压降一般在0.7V到1.5V之间。二极管的尺寸、工艺和耐压等级都会影响导通压降和反向恢复时间,大尺寸二极管通常具有较高的VF和tRR,这会造成比较大的损耗。开关二极管一般以速度划分,分为“高速”、“甚高速”和“超高速”二极管,反向恢复时间随着速度的提高而降低。快恢复二极管的tRR为几百纳秒,而超高速快恢复二极管的tRR为几十纳秒。

低功耗应用中,替代快恢复二极管的一种选择是肖特基二极管,这种二极管的恢复时间几乎可以忽略,反向恢复电压VF也只有快恢复二极管的一半(0.4V至1V),但肖特基二极管的额定电压和电流远远低于快恢复二极管,无法用于高压或大功率应用。另外,肖特基二极管与硅二极管相比具有较高的反向漏电流,但这些因素并不限制它在许多电源中的应用。

然而,在一些低压应用中,即便是具有较低压降的肖特基二极管,所产生的传导损耗也无法接受。比如,在输出为1.5V的电路中,即使使用0.5V导通压降VF的肖特基二极管,二极管导通时也会产生33%的输出电压损耗!

为了解决这一问题,可以选择低导通电阻RDS(ON)的MOSFET实现同步控制架构。用MOSFET取代二极管(对比图1和图2电路),它与电源的主MOSFET同步工作,所以在交替切换的过程中,保证只有一个导通。导通的二极管由导通的MOSFET所替代,二极管的高导通压降VF被转换成MOSFET的低导通压降(MOSFET RDS(ON)× I),有效降低了二极管的传导损耗。当然,同步整流与二极管相比也只是降低了MOSFET的压降,另一方面,驱动同步整流MOSFET的功耗也不容忽略。

IC数据资料

以上讨论了影响开关电源效率的两个重要因素(MOSFET和二极管)。回顾图1所示降压电路,从数据资料中可以获得影响控制器IC工作效率的主要因素。首先,开关元件集成在IC内部,可以节省空间、降低寄生损耗。其次,使用低导通电阻RDS(ON)的MOSFET,在小尺寸集成降压IC (如MAX1556)中,其nMOS和pMOS的导通电阻可以达到0.27Ω (典型值)

评论