基于ARM的过采样技术

2 过采样满足条件及操作步骤

对于过采样,理论上需要信号有一定噪声,并且必须近似白噪声,幅度足够大。若噪声信号不能满足前面讲述的理论要求,就需要引入噪声激励。因此,选用周期性噪声作为激励信号。同时对激励噪声有一定要求:激励噪声幅度≥1 LSB;噪声均值在添加激励噪声时必须是0.

在理解过采样理论及需要满足的条件后,出于对具体应用的考虑,设计了过采样的操作步骤,概括如下:

(1)判断被采样信号是否有噪声,如果没有噪声,则叠加周期性激励噪声。

(2)对信号进行4n次过采样(n为希望增加的分辨率位数)。如果使用片内10位ADC,希望得到14位的ADC精度,则需要44即256次10位的过采样。

(3)抽取数字序列,对各个采样值进行累加。

(4)对累加后的采样数据,若提高n位精度则右移n位,最终得到过采样值。

3 LM3S8962实现ADC过采样

3.1 Cortex-M3内核特点介绍

(1)采用ARMv7M架构,在ARMv4T架构基础上扩展了36条指令。

(2)基于哈佛结构,数据与指令可同时从存储器读取,并行执行多个操作,加快程序执行速度。与ARM7TDMI-S相比,比ARM指令每兆赫效率提高了35%,比Thumh指令效率提高了70%.

(3)带有多种睡眠和唤醒模式,实现产品的低功耗。

(4)单周期乘法、乘-加、硬件除法指令,实现快速运算。

(5)低延迟中断处理:支持8层硬件中断嵌套,末尾连锁功能,高优先级中断迟来处理。

3.2 过采样的软件实现

(1)外设初始化。

在软件实现过采样之前,必然要对各个模块进行初始化和配置。初始化定时器、ADC、UART等模块,定时器模块用来提供系统时钟周期,配置ADC的触发模式和采样速率,利用UART将测量值传递给PC,方便查验是否正确。

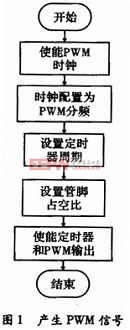

(2)产生PWM信号,作为噪声。

为了保证过采样原理应用的可靠性,引入噪声激励信号。而为了避免激励噪声出现的误差,使用内部的PWM信号发生器产生周期性和对称性很好的PWM波,作为激励噪声。产生噪声步骤如图1所示。

(3)数据的采集、滤波及抽取。

在过采样中所做的数字平均滤波仅提高了平滑度,精度却并没有增加,抽取过程才是真正意义上的提高精度。额外的K次采样,按照常规平均那样进行累加,但并不是直接将结果除以M,而是右移N位(N是期待所增加的额外精度),得到更精确的采样结果。

过采样算法如图2所示。对TI的LM3S8962芯片,将10位AD值的精度提高到12位的方法,直接调用寄存器读取函数HWREG访问FIFO缓存区,经过两次循环,将从FIFO中收集到的16个10位转换值相加,产生一个14位结果,右移2位后就得到所希望的12位AD值。

评论