基于MPC8260处理器和FPGA的DMA接口设计

1.2 CP命令控制的IDMA传输

MPC8260的IDMA还可以通过向CP命令寄存器中写入START_IDMA命令进行内部触发。每次启动传输以后

相比握手信号控制的IDMA传输,在这种方式下,PowerPC内核除了需要初始化IDMA通道以外还要以命令的形式启动每一次的传输,所以要占用多一些的内核资源。不过,在一次传输启动之后最多可以传输4 GB的数据,所以只要每次传输的数据长度比较长,内核写一个寄存器的额外开销就完全可以忽略不计。同时,由于内部命令触发方式不需要握手信号,不需要频繁地每几个字节就竞争一次总线控制权,所以这种方式的传输效率更高、传输速度更快。内部命令触发方式是以空间换时间——用前端大的缓冲区来换取传输速度的提升。

考虑到主控板上软硬件系统的瓶颈都在于总线带宽,而存储资源相对比较丰富,所以选择CP命令控制的IDMA传输作为数据流从FPGA到SDRAM的传输方式。

2 DMA传输方案设计

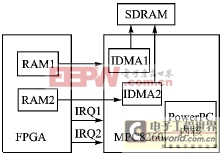

FPGA和MPC8260间的数据传输接口设计如图3所示。图中左侧FPGA,通过16位数据线、10位地址线、2根中断请求线和一些读写控制信号线连接到右侧的MPC8260。MPC8260通过64位数据线与本地内存SDRAM相连。

图3 IDMA传输设计框图

FPGA内部分配有两个大的存储空间,用于轮流缓冲从数据源接收到的数据。任何一个缓冲区收满后,继续接收的数据保存到下一个缓冲区,同时以中断的方式触发MPC8260启动相应的IDMA通道把数据传到SDRAM中。IDMA控制、数据同步和错误处理都由MPC8260完成,FPGA只负责收发数据和触发中断。下面分别介绍二者的程序设计。

2.1 MPC8260程序设计

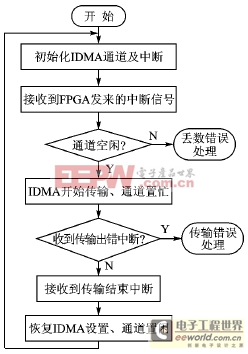

MPC8260内部的程序处理流程如图4所示。MPC8260预先初始化两个IDMA通道:通道的源地址和传输数据长度等信息与FPGA中的缓冲区一一对应。当收到FPGA的中断信号之后,如果此时对应的IDMA通道空闲,则在中断处理程序中发出CP命令开始接收数据,同时将对应的IDMA通道置忙状态;否则,在FPGA中可能发生了未读取的数据被覆盖的情况,MPC8260进入错误处理程序。在数据传输结束时由DMA控制器发送CPM内部中断到内核,在中断处理程序中一方面要恢复IDMA通道的参数设置,另一方面要把该IDMA通道置闲状态等待下一次传输的开始。

MPC8260程序的核心部分是IDMA通道设置和中断处理。

图4 MPC8260传输处理流程

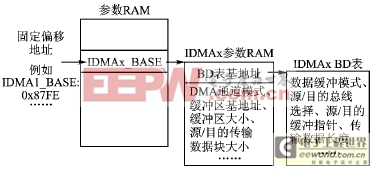

2.1.1 IDMA通道设置

与一般的DMA通道设置一样,IDMA通道设置的主要参数包括:源地址、目的地址和传输数据长度。除此之外,MPC8260的 IDMA通道设置还包括通道模式、缓冲区和中断配置等,所涉及的寄存器比较多,配置比较复杂。IDMA通道设置的逻辑结构如图5所示。

图5 IDMA通道设置的逻辑结构框图

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论