SoC测试技术面临的挑战和发展趋势

一体化测试流程

为了解决上述问题,图2所示是一种新的测试流程。它将工程设计验证测试流程与生产测试流程并行处理。其核心思想是利用虚拟原型对测试工程和IC设计过程所需要的测试程序(本身)进行查错和调试,同时,也将虚拟原型应用到生产测试流程之中,完成面向生产的测试程序的查错和调试。

为此,首先要根据工程测试结果,进行设计中的测试策略规划,目的是改进测试方法,降低测试的复杂性,并根据测试成本和复杂性对测试任务进行定义。而生产测试流程中,测试程序查错和调试的主要任务是提高成品率。

FPGA和PLD在搭建虚拟原型,完成对测试程序调试的过程中扮演着重要作用。通过利用虚拟环境,可以极大地降低对测试程序进行调试所花费的时间,减少掩膜次数,节省大量、昂贵的掩膜费用,提高成品率,并在加快产品上市时间的同时,达到芯片利润的最大化。

然而,尽管上述方法解决了缩短测试程序调试时间的问题,但是,需要在设计和生产两条线上同时对测试程序进行调试,因而资金投入上并没有显著降低,为此,Credence公司提出了利用光子进行SoC测试的新技术。

基于光子探测的SoC测试技术

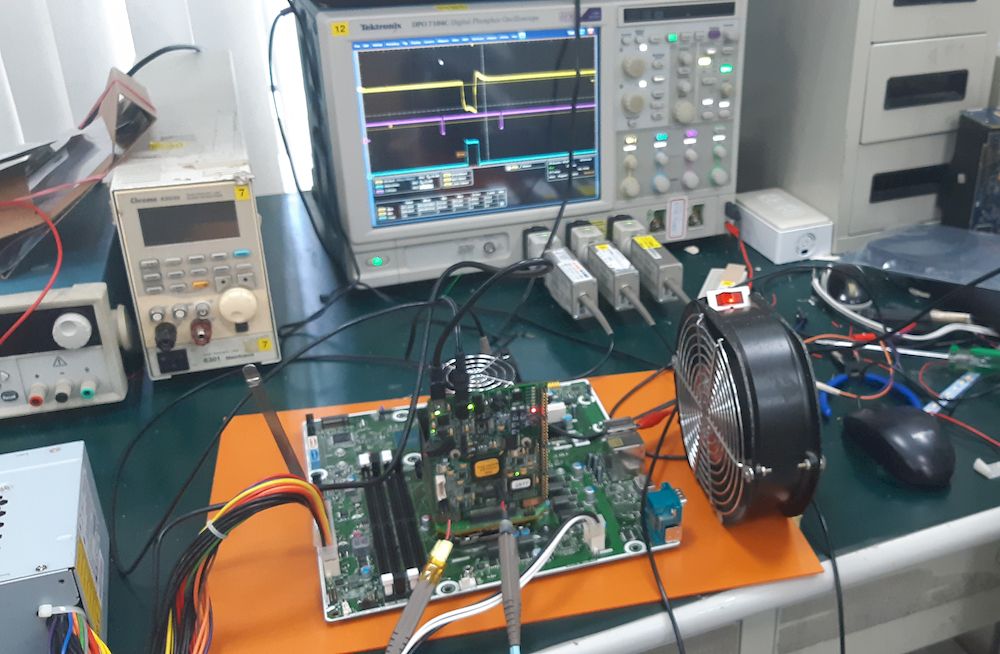

随着芯片复杂度的增加,SoC采用倒装、打线和多层金属封装的方式也越来越多,许多地方采用传统的电测手段已经相当费时费力,因此,Credence利用固态浸入透镜方法实现0.25um的成像分辨率,来完成对SoC关键节点的性能进行分析。通过测试系统配备的高速采集和数据处理能力,半导体制造商能够快速进行设计查错、故障分析和特征提取,从而极大地缩短产品上市时间并降低SoC开发的成本。

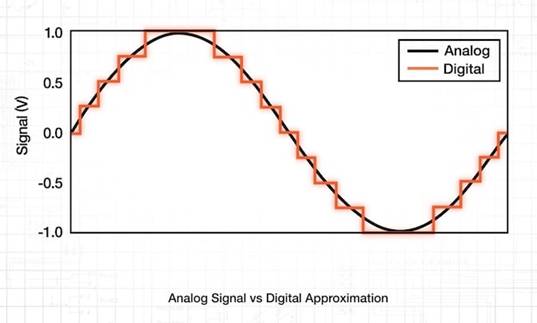

基于光子探测的SoC测试技术的基本原理是,利用脉冲信号切换产生的能量,激发半导体电路内部的电子被激发出光子,然后通过高速采集和数据处理系统,将采集的光子转化为电子信号,通过对这些电信号来分析时序特征,从而达到对SoC关键节点进行测试的目的。其目的是加速产品的上市,消除不必要的多次设计修改和不必要的流片循环。

本文小结

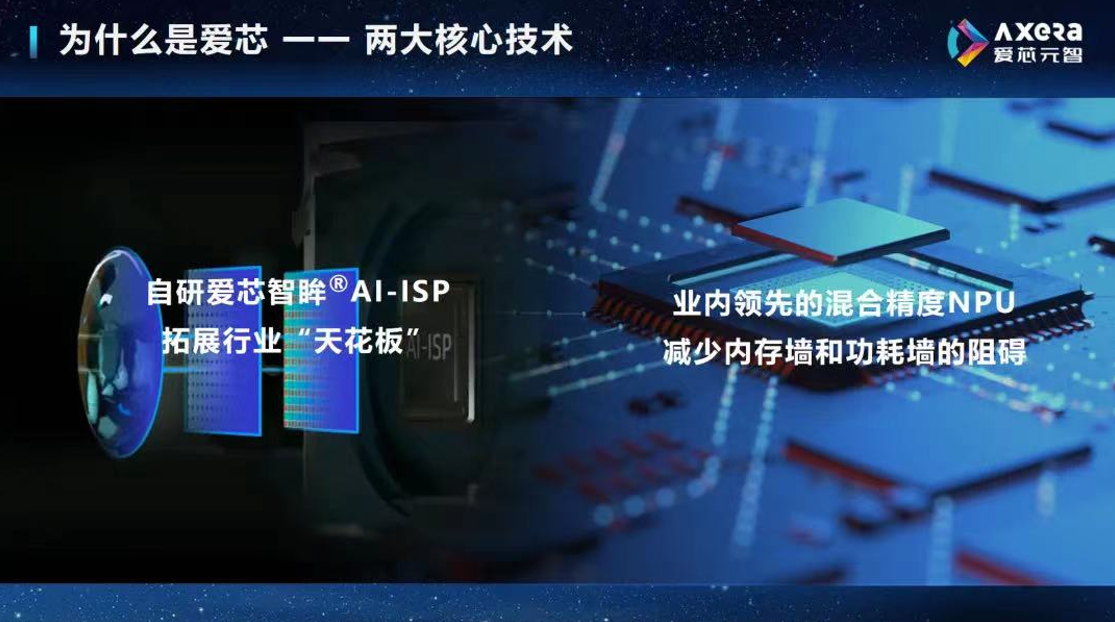

SoC技术是21世纪初以来迅速发展起来的超大规模集成电路的主流技术,是电子器件持续集成的最高境界。SoC采用先进的超深亚微米CMOS工艺技术,从整个系统的角度出发,将处理机制、模型算法、嵌入式软件等各层次电路直至器件的设计紧密结合在单个芯片上,完成整个系统的功能。

随着SoC应用的日益普及,在测试程序生成、工程开发、硅片查错、量产等领域对SoC测试技术提出了越来越高的要求,掌握新的测试理念、新的测试流程、方法和技术,是应对消费电子、通信和计算等领域SoC应用对测试技术提出的挑战,适应测试和组装外包发展趋势的必然要求。对于中国集成电路测试人员来说,了解中国目前SoC测试技术发展面临的挑战和发展方向,掌握市场的动态至关重要,表1所示为中国目前已经具备SoC测试能力的测试中心和实验室的一览表。

评论