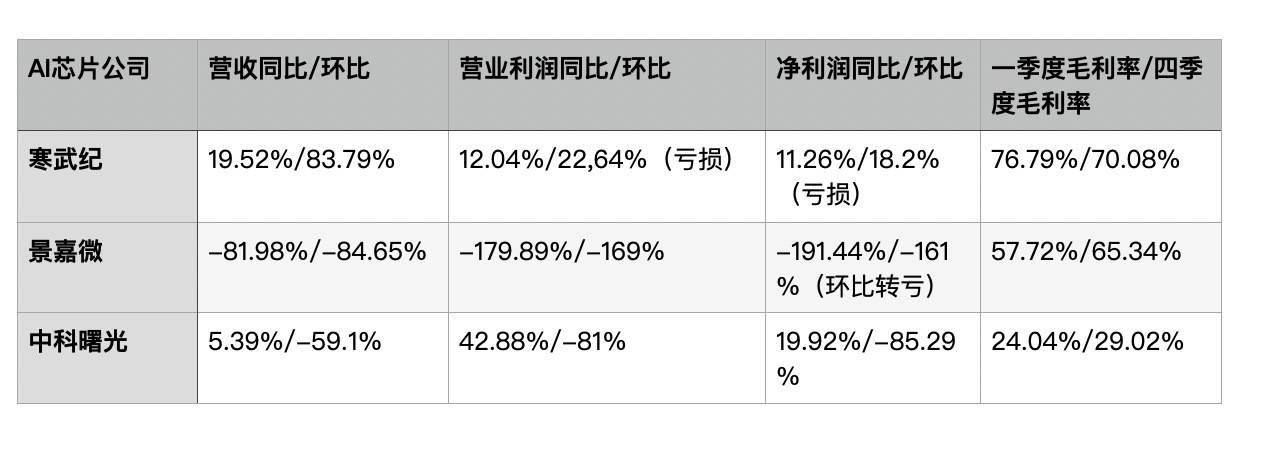

基于ISP1362的U盘MP3播放器设计

主要芯片简介

AT89C51SND1是ATMEL推出的基于8位C51 MCU内核的MP3解码器芯片。它内置MP3硬件解码器,支持48kHz、44.1kHz、32kHz、24kHz、22.05kHz及16kHz采样频率,具有重低音、中音、高音均衡控制和重低环绕声效果。它可以适应市场上不同DAC的可编程音频输出接口,兼容PCM和I2S格式。内置2304B RAM和64KB Flash程序空间,方便用户增加复杂的功能。并通过内置锁相环提供MP3和音频时钟以及USB时钟。

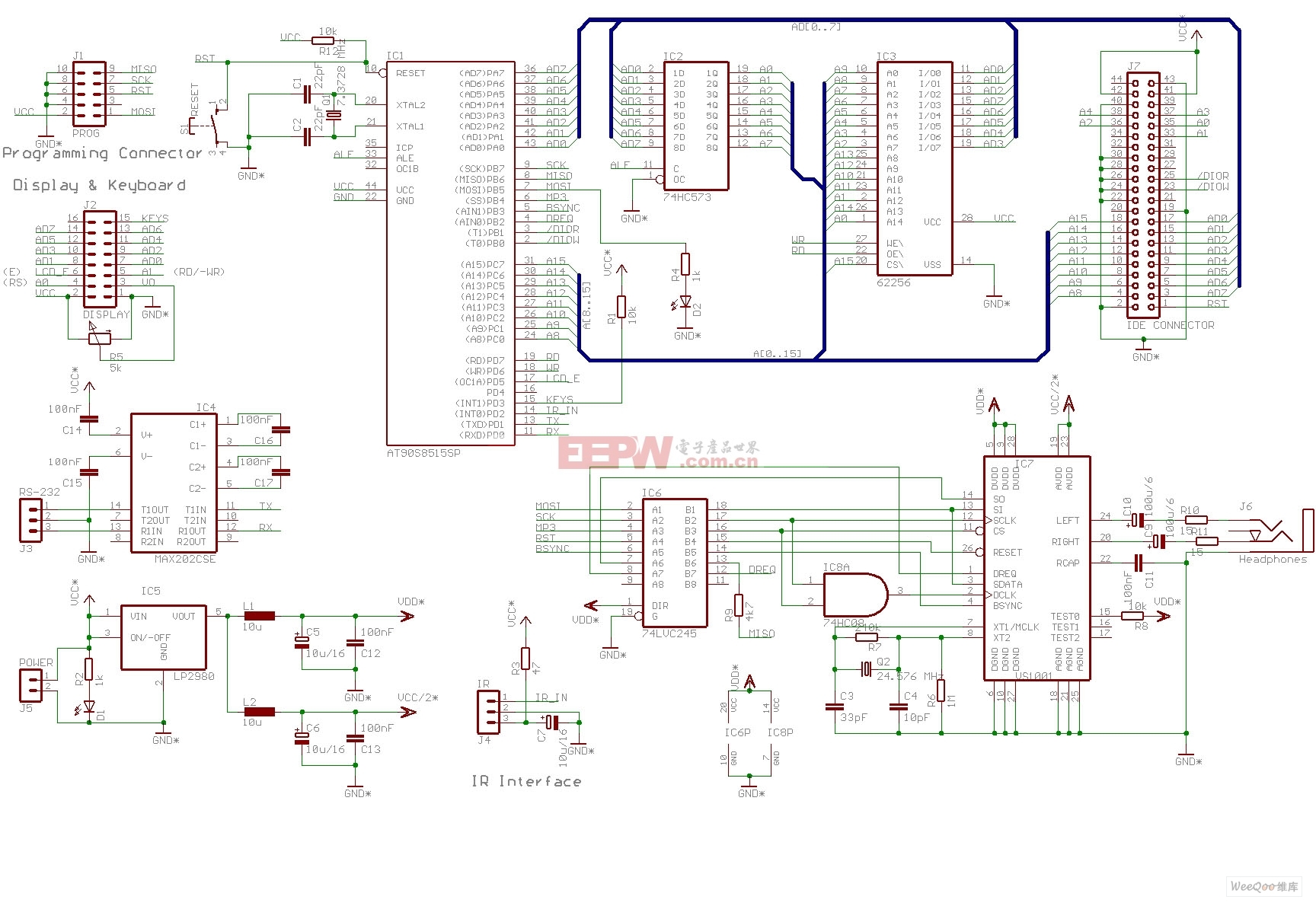

要想读取U盘,USB主机控制器必不可少。为了将来进一步升级系统,本文选用了功能强大的USB-OTG芯片ISP1362。ISP1362在单芯片上集成了OTG控制器、高级主机控制器和外设控制器。ISP1362的OTG控制器完全兼容USB2.0以及On-The-Go Supplement 1. 0协议,主机和设备控制器兼容USB 2. 0协议,并支持12Mbps的全速传输和1.5Mbps的低速传输。

图1 系统框架图

系统硬件结构

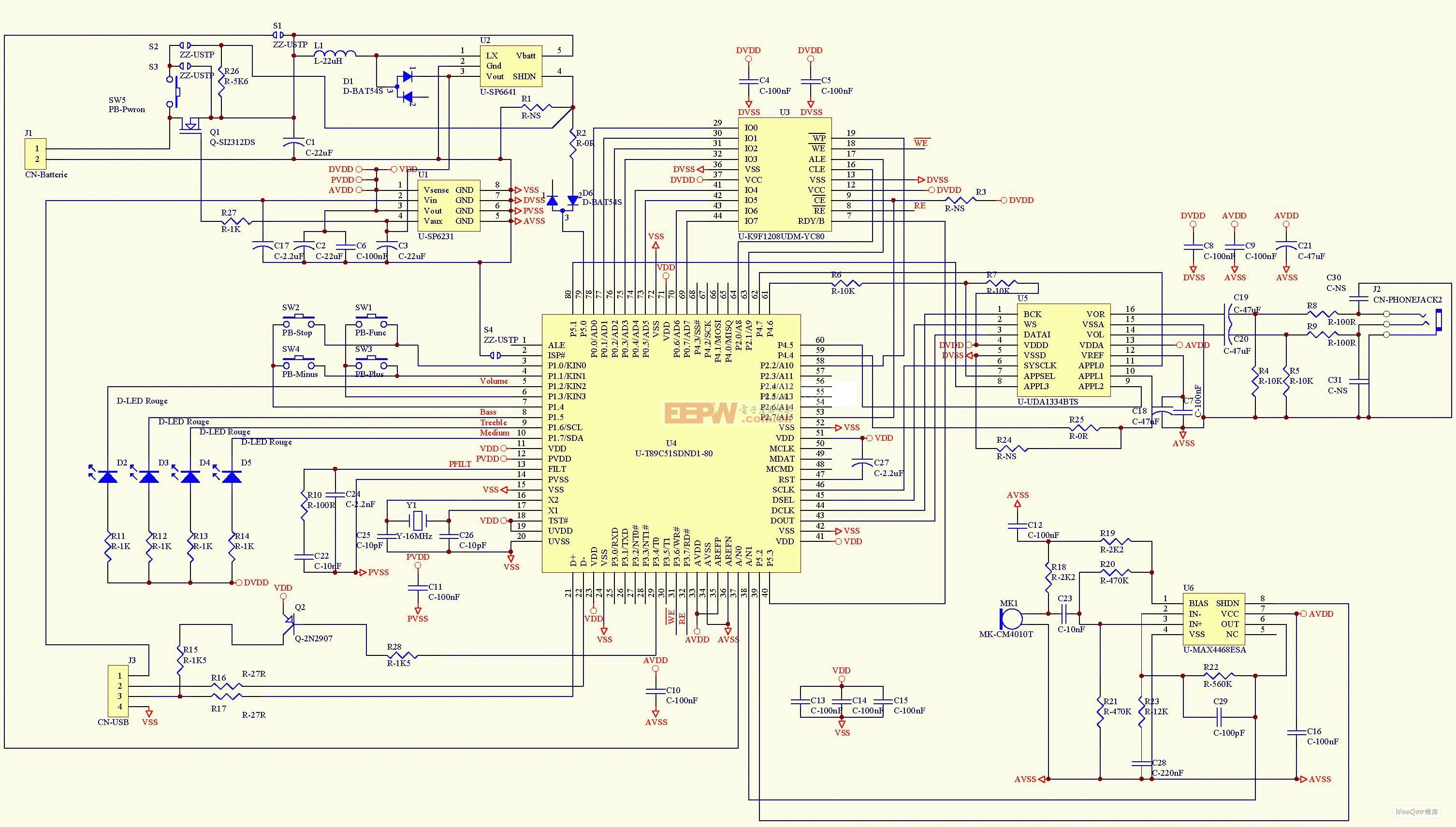

整个系统的搭建围绕AT89C51SND1进行,如图1所示。由于其内部具有硬件解码器,因此电路构成并不复杂。首先由单片机控制ISP1362,将U盘中的MP3文件读取出来,送到硬件解码器进行解码。解码之后由数字音频接口将数字信号传送至音频DAC CS4330,转换之后产生音频信号。由于DAC输出的信号功率有限,在后端又加入了运算放大器,经过放大之后的信号就可以直接输出给音箱或耳机等设备了。

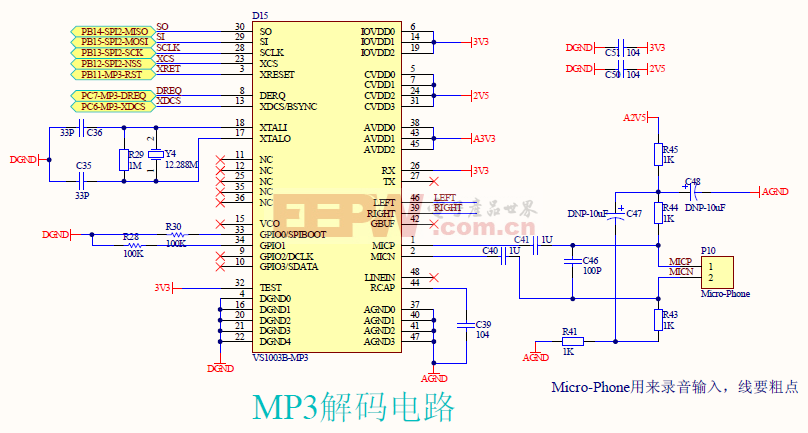

AT89C51SND1是基于51内核的单片机,因此,最小系统结构非常简单。除了传统单片机的晶振和复位电路之外,还有PLL滤波电路和USB接口电路,如图2所示。

图2 PLL滤波电路及USB接口电路

ISP1362是16位总线结构,不能直接和8位单片机接口。因此,将单片机的P0和P2口一同作为数据总线接至ISP1362的16位总线上,将 、、分别接到单片机的P3.4、P3.7和P3.6,通过仿真读写时序控制它的数据读取等操作。

除了这些基本的总线连接,ISP1362还需要连接一些特殊的控制引脚:

A0:用于决定控制器处于命令状态还是数据状态:0表示数据状态,1表示命令状态;

A1:用于决定控制器工作于主机还是设备控制模式:0表示处于主机控制(HC) 模式;1表示处于设备控制(DC) 模式。

接至MCU的P1.5。P1.5=0时表示处于OTG工作状态,P1.5=1则表示处于非OTG状态。

INT1_USB、INT2_USB分别接至MCU的INT0和INT1引脚,用以产生中断。

ISP1362有两个USB端口,分别是OTG端口和主机端口。因为OTG端口包含了主机功能,所以系统中使用OTG端口来连接U盘。根据USB2.0协议,USB主机需要2个15k降南吕缱瑁玂TG端口同时又可作为设备端口使用,而设备是没有下拉电阻的。因此ISP1362提供了“软连接”机制,通过内部的寄存器来控制电阻的连接与否。所以在硬件设计时并不需要在外部加下拉电阻。而 为开漏输出,因此加入了一个10kW的上拉电阻R14_USB。如图3所示。

图3 OTG端口电路图

AT89C51SND1C及ISP1362的初始化

在开始播放MP3文件之前,需要一系列初始化操作。这些操作是通过设置AT89C51SND1C及ISP1362内部的相关寄存器来完成的。

AT89C51SND1C的初始化

为了正常播放MP3文件,首先要对主控制器AT89C51SND1C进行以下几方面的设置。

锁相环初始化

MP3解码器和音频输出接口使用的都是内部锁相环提供的时钟。锁相环的初始化是通过设置PLLCON、PLLNDIV和PLLNDIV来完成的。其输出频率的计算公式为:PLLclk=OSCclk

评论