一种嵌入式USB2.0主机控制器IP核的研究与设计

CPU 工作在12~ 160MHz 时钟频率。 CPU 模型通过读命令文件master. cmd 来触发嵌入式USB 主机开始配置寄存器的读写。

3. 2 存储器模型

在IN 传输中, 存储器模型通过DMA 通道从嵌入式USB 主机中数据缓冲器模块读出数据, 并将读出的数据写入data. dmp 文件中, 在OUT 传输中,嵌入式USB 主机通过DMA 通道读存储器模型中的数据到数据缓冲器, 而存储器模型中数据是存放在ehin. dat 文件中。

3. 3 PHY 模型

此处的PHY 模型包括USB 主机方的PHY1 和USB 设备方的PHY2, 本设计主要用于高速和全速的数据传输, 所以接入的PHY 模型为2. 0 版本。 它主要功能是串行数据与并行数据之间相互转换, 因为在嵌入式USB 主机中都为并行数据, 而在USB电缆中是以串行数据传输的。

3. 4 USB 设备模型

此模块通过读命令文件dev1. cmd 来控制USB信息包的发送与接收, 若IN 传输时设备模型将dev1 sen. dat 文件中所包含的数据发送给主机, 在OUT 传输中将主机输出的数据也储存在dev1rcv. dat 中。

为了方便观察仿真结果, 设计中还加入了一个验证传输中数据对错的模块, 在IN 传输中将设备模型中从dev1 sen. dat 发出的数据与USB 主机收到的数据进行对比, 在OUT 传输时将进入USB 主机的数据与设备模型中dev1 rcv. dat 收到的数据进行对比, 由此可以清楚的看出在USB 主机与设备之间是否正确传输数据。

这里采用nc2verilog 分别对高速和全速中IN,OUT 传输以及枚举过程进行的功能仿真, 部分仿真波形如图5、图6 所示。 可以看到: 全速和高速的整个枚举过程中状态机enmumerate state 的变化直到传输使能; 整个主控制状态机mast ectrlst 中各状态的转换; 在每次数据传输中utmtxready, utm rxactive, utm rxvalid 以及utm rx2validh 的跳变过程。 在高速和全速的仿真中, 验证先IN 传输再OUT 传输, 即先从USB 设备模型中dev1sen. dat 文件中读出数据进行4 个信息包的IN 传输, 然后执行4 个信息包的OUT 传输。

图5 高速数据批量传输仿真图

图6 全速数据批量传输仿真图

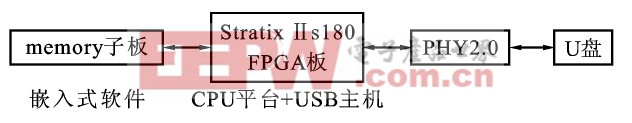

4 FPGA 验证

FPGA 验证环境如图7 所示, 验证中外接一块USB2. 0 的PHY 子板和memory 子板, 其中FPGA芯片为Altara 公司的stratixIIs180, 其中实现嵌入式USB 主机IP 核和CPU 平台, memory 子板用来实现嵌入式软件, 在验证时分别接入支持高速和全速的U 盘作为设备, 对U 盘进行了数据的读写, 不管是在高速下还是在全速下都能正常完成U 盘的读写过程, 并与预期的读写数据一致。

图7 嵌入式USB2. 0 主机控制器验证环境

从nc2verilog 的功能仿真和FPGA 验证表明, 此嵌入式USB2. 0 主机控制器IP 核成功地实现了高速和全速下数据传输。

5 结束语

此嵌入式USB2. 0 主机控制器IP 核在设计中采用了乒乓缓冲模式提高了数据传输的速度, 还采用了DMA master 和slave 模式, 很大程度的减小了CPU 的要求, 在仿真和FPGA 验证中分别采用了CPU 频率为12MHz 和160MHz, 此IP 核都通过了功能验证。 目前已流片, 且通过芯片验证。 因此可以说此IP 核能够独立地用于数码相机, MP3 播放器里。 这样, 这些嵌入式的主机就可以直接和移动硬盘、打印机等设备连接用了, 不需要通过PC 机来进行相互的文件和数据交换, 实现了脱离PC 机的梦想, 方便了更多使用者。

评论