双供电DSP电源设计的总线冲突

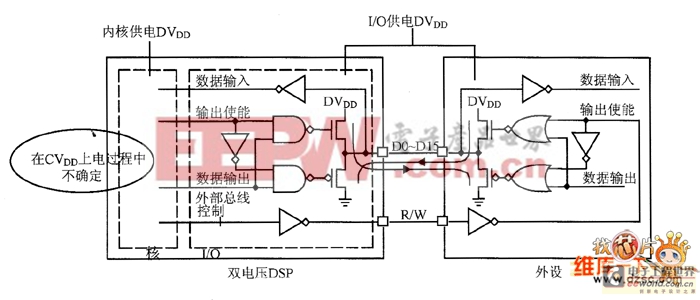

实际上在DSP系统设计时,防止DSP的IJO引脚同外设之间的总线冲突是系统设计的一个重要方面,需要控制内核和IJO的上电次序。由于总线的控制逻辑位于DSP内核模块,I/O供电先于内核供电会使DSP和外设同时配制成输出功能引脚。如果DSP与外设输出的电平相反将会产生总线冲突。图1给出了一个简单的双向口,此时会有较大的电流流过相反电平的通道。因此,系统设计时要求内核和外部I/O同时供电,从而避免总线控制信号处于不定状态时的冲突。如果内核先于I/O掉电,总线控制信号又处于不定的状态,也会导致有较大的电流流过I/O和DSP内核。因此,正确的上电、掉电次序(内核先上电后掉电)是保证系统可靠性,延长器件使用寿命的一种必要措施。

图1 双向端口总线冲突示意图

评论