一种用于家庭可视门铃的无线视频通信系统

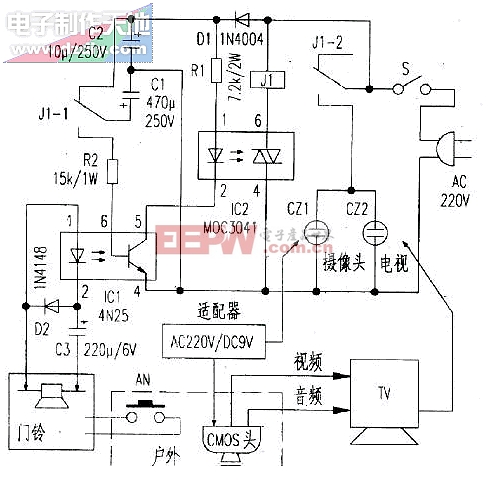

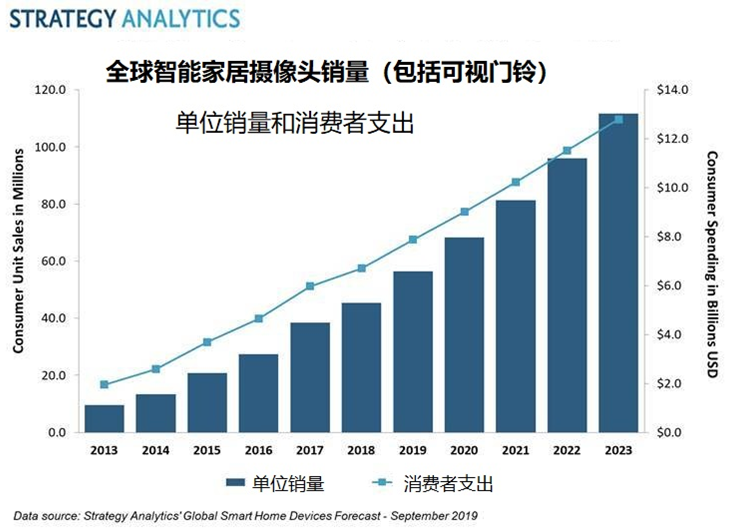

摘要:介绍一种用于家庭可视门铃的无线视频通信系统。该系统将数字摄像头采集的图像数据经过滤波、放大等处理,调制到2.4GHz的载波上,由无线收发模块发射击去;接收端将该视频数据解调还原,并传送到显示模块,在LCD显示出来。 关键词:nRF2401无线视频信号 AT89C52 摄像头7260 目前,国内安装的可视门铃多数是有线的,或是通过类似于电视系统的调幅或调频方式来发送图像的。出于成本的考虑,这些可视门铃系统传输距离受限制,信号质量不高,抗干扰性差。随着用户要求的提高,尤其是在大型别墅中,门铃和图像接收端相距较远,这就需要将有线变为无线,模拟信号调幅或调频无线传输变为数字信号调制(FSK,QFSK,GFSK)无线传输。FSK(Frequency Shift Keying)即键控频移,QFSK(Quadrature Frequency Shift Keying)即正交键控频移,GFSK(Guassian Frequency Shift Keying)即高斯键控频移。通过系统的数字化,图像信号质量得到提高,抗干扰性得到大大加强;同时,整个系统的体积相比其它的传输方式将会减小很多,因此,具有广泛的商业应用价值和发展前景。

本文引用地址://m.amcfsurvey.com/article/256145.htm

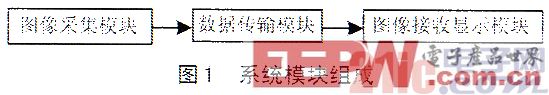

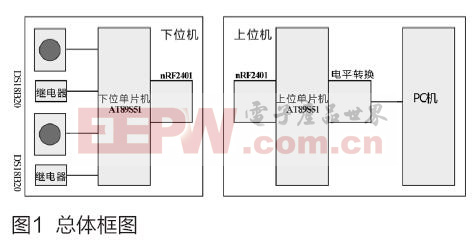

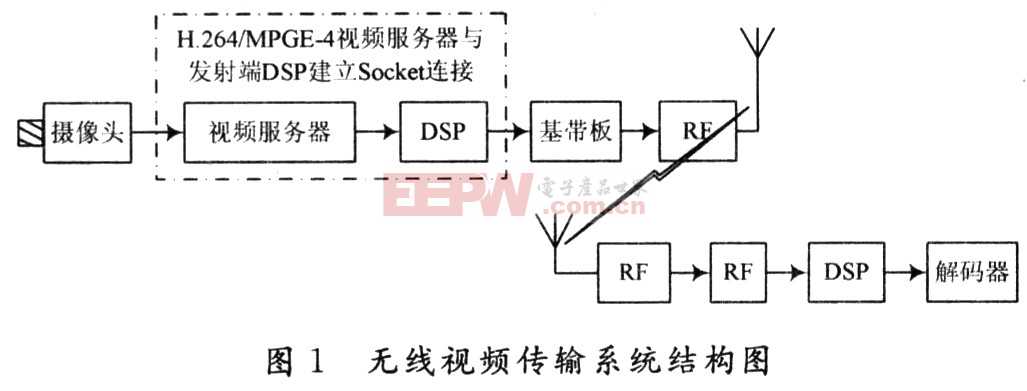

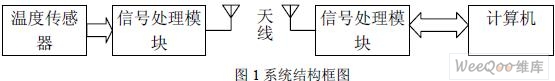

由于我们的系统用于别墅单用户的可视门铃,因此对图像的连续性要求不高。设想一直,在户主听到门铃响,再到门口查看监视器的画面最少需要3s。只需要传输 1帧图像到监视终端,让户主看到来访者是谁就可以了。因此由于成本的原因,我们会把采集到的图像直接传输出去而中间不会加上昂贵的图像压缩解压缩芯片。 整个数字无线视频通信系统主要由三个模块构成:图像采集模块、数据传输模块、图像接收显示模块,如图1所示。

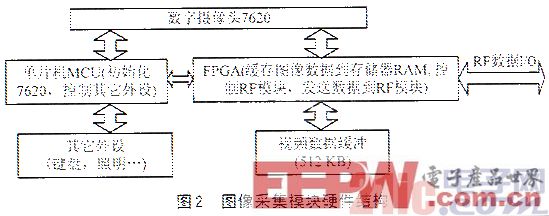

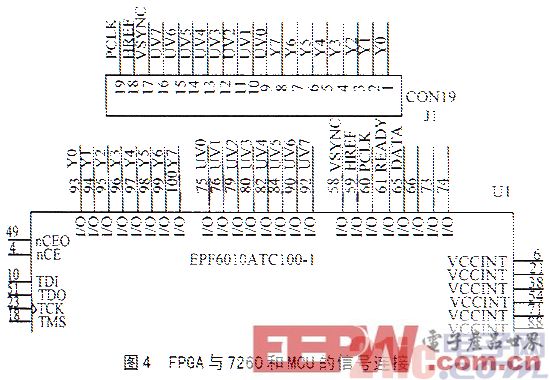

1 图像采集模块 该模块的硬件框图如图2所示。 摄像头7620是256色30万像素的CMOS摄像头。它输出并行16位图像信号,包括8位的色度信号、8位的亮度信号以及场同步与行同步信号。1帧图像(640%26;#215;480)的尺寸是640%26;#215;480%26;#215;16=4 915 200(位) 如果以RF发送模块nRF2401的最大速度1Mbps来计算,发送1帧图像所要的时间为 4 915 200/1 000 000=4.9152(s) 这显然太长了。不过,7620还有一种工作模式就是,通过降低分辨率来减少图像尺寸。这种模式提供了320%26;#215;240的图像。这样,图像数据不到3s就可以到达接收端,满足可视门铃的要求。 图3 8位色度信号、8位亮度信号以及场同步与行同步信号先通过FPGA缓存到RAM,同时转换为异步串行数据,通过RF模块发送。图3是7620的工作时序。 图3中,Y信号是8位亮度信号,UV是8位色度信号。VSYNC是场同步信号,HREF是行同步信号。 FPGA的工作是完成图像数据的缓存控制以及启动RF模块发送图像数据。这里,采用Altera公司的EPF6016。它是一颗16000门的FPGA。图4为FPGA与摄像头7260、MCU以及RF模块的连接示意图。 图4中,U1为EPF6016ATC100,J1是FPGA与摄像头7260的连接插座。Y、UV、VSYNC和HREF的定义如前,READY是MCU 对FPGA的控制信号,DATA是FPGA与RF模块之间的串行数据线。

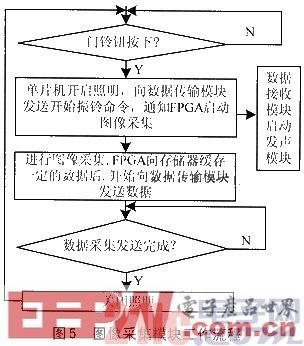

当用户按下门铃,MCU收到命令开启照明灯,同时初始化摄像头7260,并发送READY信号给FPGA,通知其准备接收图像信号。由7260的工作时序可以看到,当摄像头采集到一帧图像后,VSYNC便发送1个高电平,FPGA准备接收信号。1帧图像由很多行组成。这些行在场同步信号VSYNC的两个高电平之间传送。而每一行的信号传输现时由HREF同步。当HREF的上升沿来到后,FPGA开始接收图像数据。在PCLK的上升沿,每一行的图像数据通过 Y口和UV口送出,从时序图可以看到1行包括640个点。 FPGA需要将收到的图像缓存到512KB的RAM,需要有20位的地址信号线和8位的数据信号线。 FPGA采集到的图像信号是并长的数字信号。要将这些信号发射出去,还需要转化为异步串行数据,这个工作由FPGA来完成。我们所规定的异步串行通信协议和通用的RS232协议类似: 没有信号时,DATA线为高电平;要传送数据的时候,先发送1个低电平脉冲(起始位),紧接着2个字节的数据(Y[7:0],UV[7:0],然后再发送 1个高电平脉冲(停止位)。1帧有效的串行数据就由这几部分构成。 微控制器MCU主要完成以下几个任务: ①初始化数字摄像头7620; ②控制其它外设,接收和处理键盘命令,控制照明设备的开启等; ③与FPGA协同工作,并提供人机接口。 MCU采用常用的AT89C52。图像采集模块的工作流程如图5所示。

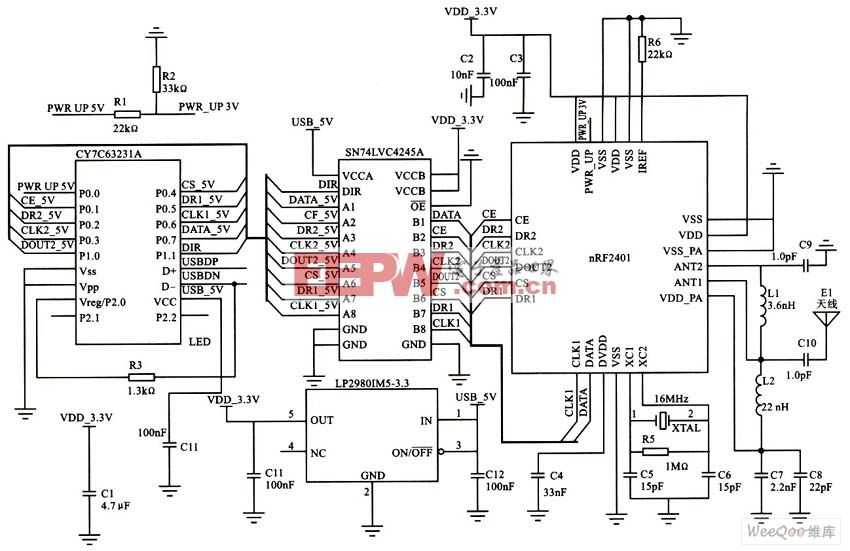

2 图像传输模块 图像传输模块(RF module)由一块单片无线收发芯片nRF2401完成。NRF2401工作在2.4~2.5G ISM频带,集成了频率综合器、功率放大器、晶体振荡器和调制器。由于nRF902使用了晶体振荡器和稳定的频率合成器,因此频率漂移很低。电源电压范围为2.4~3.6~,输出功率为10dBm,电流消耗仅9mA。输出功率和频偏可通过外接电阻进行编程。

输出信号为调制的GFSK(高斯键控频率信号),很容易通过8线串行I/O口进行收发。图6为nRF2401在无线通信中扩展的外围电路。 通过PWR-UP、CE、CS引脚的选择,nRF2401可以工作在激活/等待/节能模式。这里,使nRF2401工作在激活的突发脉冲(shock burst)模式。该模式使用片上FIFO。在不使用MCU控制数据操作情况下,能以极低的功耗运行数字部分而又以极快的速度(最高为1Mbps)传输数据,从而大大减少了电流消耗,降低了系统成本并且减少了传输时的“空中冲突”冒险。 FPGA送来的异步串行数据经过nRF2401内部的RF带通滤波、低噪声放大、频率综合和脉冲放大,被调制成2.4GHz上的GFSK信号,完成图像信号的传输。 3 图像接收显示模块 图像接收显示模块主要由三部分组成:图像接收、图像转换和暂存、图像显示。如图7所示。 (1)图像接收 图像接收部分也是由无线收发芯片nRF2401完成。nRF2401可以同时发射1组、接收2组信号。在突发脉冲模式下,将RX和CE置高,200μs的建立时间后,nRF2401开始监测空中,接收到有效的数据包后解调为原来的数字信号,送以端头、地址和CRC位,MCU发出中断命令,DR1拉高。 MCU也可以置CE为低来中止RF字的接收,同时为载入数据输出适当频率的时钟。当所有的数据载入后,将DR1拉低,准备接收下一个数据包。 图6 (2)图像转换和暂存 nRF2401传输给FPGA的异步串行数据,经过FPGA转换为并行数据并暂存到缓冲区(512KB的外部RAM),收到MCU的命令后将RAM内部的数据送到LCD显示。当整幅图像都被接收以后,FPGA将存储的视频发送到LCD控制器SED1353。出于安全性的考虑,系统同时还外挂有2MB的内存事保存视频历史记录。图像转换和暂存的过程,其实是前面图像采集的逆过程。接收部分FPGA的设计与发送部分类似,这里不再详述。

pa相关文章:pa是什么

通信相关文章:通信原理

摄像头相关文章:摄像头原理

评论