嵌入式系统基础之:ARM处理器硬件开发平台

S3C2410X系统结构图如图4.11所示。

下面依次对S3C2410X的系统管理器、NandFlash引导装载器、缓冲存储器、时钟和电源管理及中断控制进行简要讲解,要注意,其中所有模式的选择都是通过对相关寄存器特定值的设定来实现的,因此,当读者需要对此进行修改时,请参阅三星公司提供S3C2410X用户手册。

1.系统管理器

S3C2410X支持小/大端模式,它将系统的存储空间分为8个组(bank),其中每个bank有128MB,总共为1GB。每个组可编程的数据总线宽度为8/16/32位,其中bank0~bank5具有固定的bank起始地址和结束地址,用于ROM和SRAM。而bank6和bank7是大小可变的,用于ROM、SRAM或SDRAM。这里,所有的存储器bank都具有可编程的操作周期,并且支持掉电时的SDRAM自刷新模式和多种类型的引导ROM。

2.nandflash引导装载器

S3C2410X支持从nandflash存储器启动,其中,开始的4KB为内置缓冲存储器,它在启动时将被转载(装载or转载)到SDRAM中并执行引导,之后该4KB可以用作其他用途。

图4.11S3C2410X系统结构图

|

Flash是一种非易失闪存技术。Intel于1988年首先开发出NorFlash技术之后,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年东芝公司发布了NandFlash结构,强调降低每比特的成本、更高的性能,并且像磁盘一样可以通过接口轻松升级。 NorFlash的特点是芯片内执行(ExecuteInPlace),这样应用程序可以直接在Flash闪存内运行,而不必再把代码读到系统RAM中。NorFlash的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 Nandflash结构能提供极高的单元密度,可以达到高存储密度,NAND读和写操作采用512字节的块,单元尺寸几乎是nor器件的一半,同时由于生产过程更为简单,大大降低了生产的成本。NAND闪存中每个块的最大擦写次数是100万次,是NorFlash的10倍,这些都使得NandFlash越来越受到人们的欢迎。 |

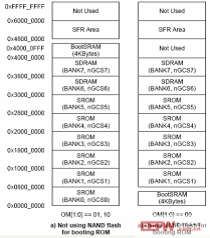

同时,S3C2410X也支持从外部nGCS0片选的Norflash启动,如在优龙的开发板上将JP1跳线去掉就可从NorFlash启动(默认从NandFlash启动)。在这两种启动模式下,各片选的存储空间分配是不同的,如图4.12所示。

图4.12S3C2410两种启动模式地址映射

3.缓冲存储器

S3C2410X是带有指令缓存(16KB)和数据缓存(16KB)的联合缓存装置,一个缓冲区能够保持16字的数据和4个地址。

4.时钟和电源管理

S3C2410X采用独特的时钟管理模式,它具有PLL(相位锁定环路,用于稳定频率)的芯片时钟发生器,而在此,PLL又分为UPLL和MPLL。其中UPLL时钟发生器用于主/从USB操作,MPLL时钟发生器用于产生主时钟,使其能以极限频率203MHz(1.8V)运行。

S3C2410X的电源管理模式又分为正常、慢速、空闲和掉电4种模式。其中慢速模式为不带PLL的低频时钟模式,空闲模式始终为CPU停止模式,掉电模式为所有外围设备全部掉电仅内核电源供电的模式。

另外,S3C2410X对片内的各个部件采用独立的供电方式。

n 1.8V的内核供电。

n 3.3V的存储器独立供电(通常对SDRAM采用3.3V,对移动SDRAM采用1.8/2.5V)。

n 3.3V的VDDQ。

n 3.3V的I/O独立供电。

由于在嵌入式系统中电源管理非常关键,它直接涉及功耗等各方面的系统性能,而S3C2410X的电源管理中独立的供电方式和多种模式可以有效地处理系统的不同状态,从而达到最优的配置。

5.中断控制

中断处理在嵌入式系统开发中非常重要,尤其对于从单片机转入到嵌入式的读者来说,与单片机中简单的中断模式相比,ARM中的中断处理要复杂得多。如果读者无相关基础,建议先熟悉相关的基础概念再进行下一步学习。

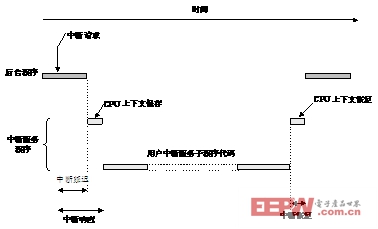

首先给出了一般的中断处理流程,如图4.13所示。

图4.13一般中断处理流程

S3C2410X包括55个中断源,其中有1个看门狗定时器中断、5个定时器中断、9个通用异步串行口中断、24个外部中断、4个DMA中断、2个RTC(实时时钟控制器)中断、2个USB中断、1个LCD中断和1个电池故障。其中,对外部中断源具有电平/边沿两种触发模式。另外,对于非常紧急的中断可以支持使用快速中断请求(FIQ)。

S3C2410X的中断处理流程(该图摘自S3C2410X用户手册)如图4.14所示。

图4.14S3C2410X中断处理流程

图中的SUBSRCPND、SRCPND、SUBMASK、MASK和MODE都是与中断相关的寄存器,其中SUBSRCPND和SRCPND寄存器用来表示有哪些中断被触发了和是否正在等待处理(pending);SUBMASK(INTSUBMSK寄存器)和MASK(INTMSK寄存器)用于屏蔽某些中断。

图中的“Requestsources(withsub–register)”表示的是INT_RXD0、INT_TXD0等11个中断源,它们不同于“Requestsources(withoutsub–register)”的操作如下:

(1)“Requestsources(withoutsub–register)”中的中断源被触发之后,SRCPND寄存器中相应位被置1,如果此中断没有被INTMSK寄存器屏蔽、或者是快中断(FIQ)的话,它将被进一步处理。

(2)对于“Requestsources(withsub–register)”中的中断源被触发之后,SUBSRCPND寄存器中的相应位被置1,如果此中断没有被SUBMSK寄存器屏蔽的话,它在SRCPND寄存器中的相应位也被置1。在此之后的两者的处理过程是一样的。

接下来,在SRCPND寄存器中,被触发的中断的相应位被置1,等待处理。

(1)如果被触发的中断中有快中断(FIQ)——MODE(INTMOD寄存器)中为1的位对应的中断,则CPU的FIQ中断函数被调用。注意:FIQ只能分配一个,即INTMOD中只能有一位被设为1。

(2)对于一般中断IRQ,可能同时有几个中断被触发,未被INTMSK寄存器屏蔽的中断经过比较后,选出优先级最高的中断,然后CPU调用IRQ中断处理函数。中断处理函数可以通过读取INTPND(标识最高优先级的寄存器)寄存器来确定中断源是哪个,也可以读INTOFFSET寄存器来确定中断源。

小知识

小知识

评论