UMC 设计实现平台新增 Calibre 可靠性验证和交互式客制化设计验证功能

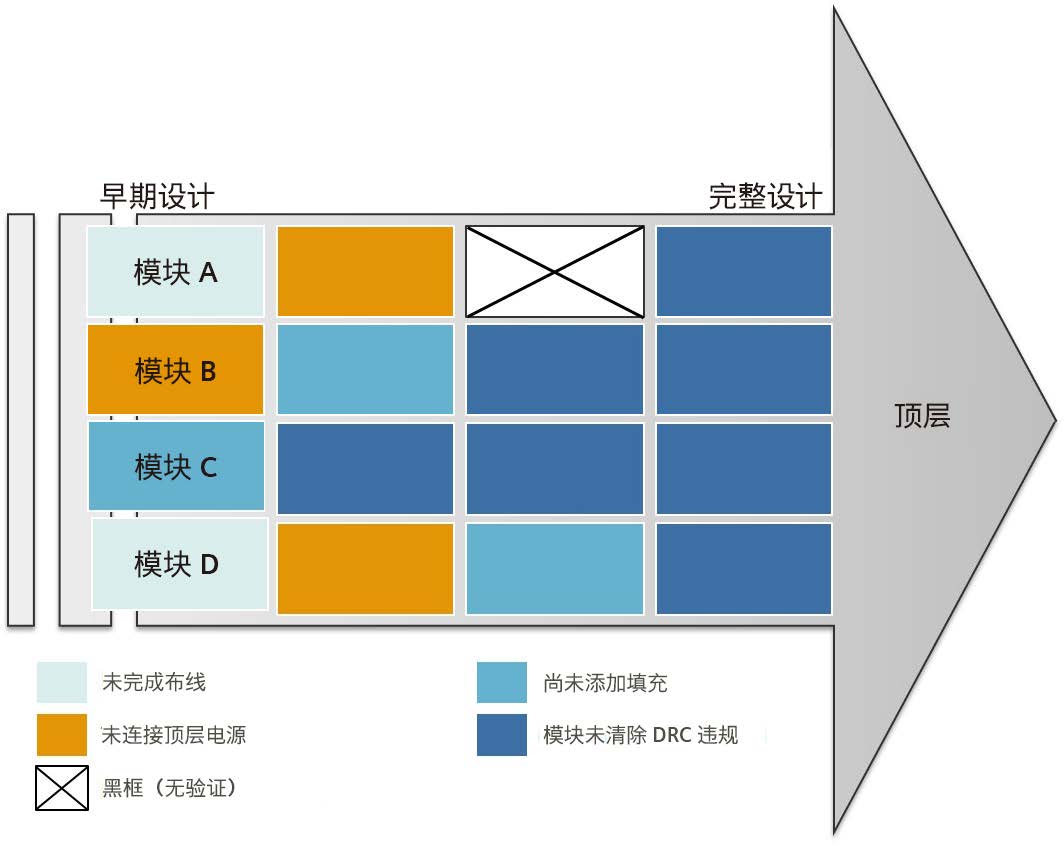

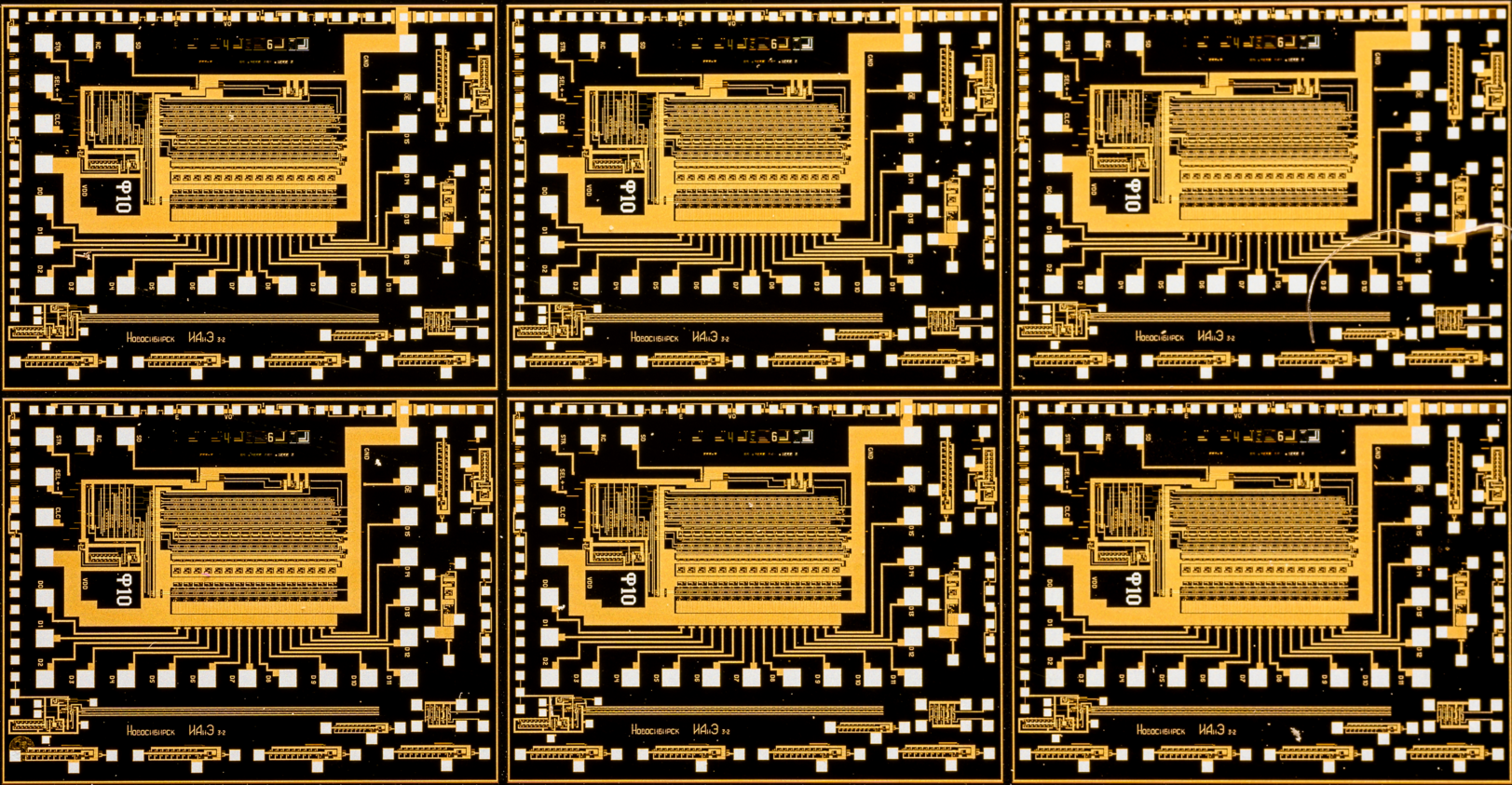

Mentor Graphics公司今天宣布,United Microelectronic Corporation (UMC) 正在为其客户开发一套新的IC 可靠性参考流程。这一全新的流程是基于Calibre® PERC™可靠性验证平台而开发,可检测细小的设计缺陷,如可能引起场内(in-field)故障的静电放电(ESD) 保护电路缺失,从而帮助客户提高其IC 产品的长期可靠性。此解决方案包括由UMC和 Mentor Graphics 正在联合开发的预先定义的检查,目标客户为采用UMC28 nm工艺的所有共同客户。UMC 预计将在今年年底首次推出其可靠性检查。

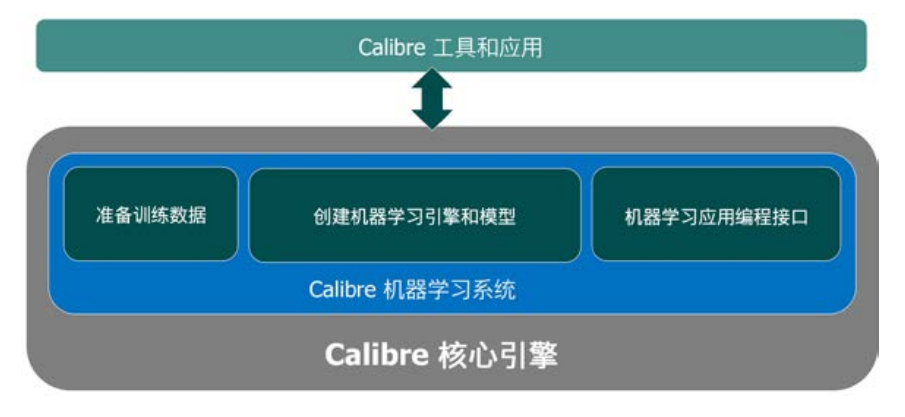

本文引用地址://m.amcfsurvey.com/article/276968.htm此外,UMC 还在其设计实现平台中新增了CalibreRealTime解决方案。UMC模拟结果指出,在客制化设计中采用CalibreRealTime来找出和解决物理验证问题可以提高两倍以上的生产效率。

CalibreRealTime可让设计工程师在各自常使用的布局编辑软件绘制电路布局图时,以实时交互的方式查看验证错误。由于此工具采用UMC 的标准签核Calibre 设计套件,UMC 客户也可实现UMC 所宣称的相同的效率提升。

UMC 硅智财研发暨设计支持部处长林世钦表示:“电路可靠性检查需要有特殊功能的工具。设计工程师需要自动化系统来识别诸如ESD保护电路等特定的电路结构,并且能够计算内部电压值,以确保电路中每个节点的电压维持在限定范围。与此同时,提高生产效率是UMC 内部设计团队和UMC 客户一致努力的方向。藉由在设计实现平台中加入Calibre® PERC™ 和Calibre RealTime工具,我们就能同时满足这些需求。”

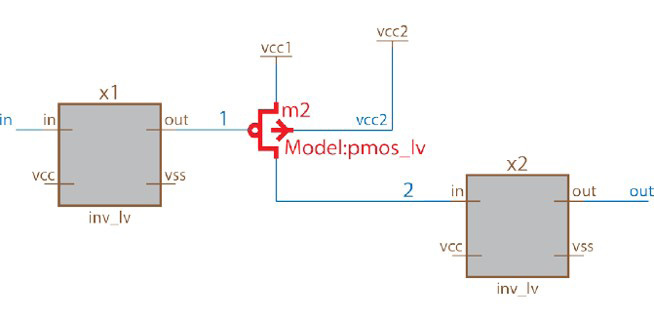

Calibre® PERC™ 解决方案提供了一项独特的功能,可用来检查物理布局和原理图网表中的信息,这些信息包括各种组件的类型以及连接关系。这种逻辑驱动布局(LDL) 分析能力可确保所有设计,包括UMC IP 库和客户设计符合UMC ESD 和电气过载(EOS) 设计规则。部分重要的 ESD/EOS 保护技术包括:

• 在所有必要位置验证有无ESD 保护电路

• 确保从IO Pad 到电源/地Pad的ESD 路径互连的电阻最小,且可以承受较大的人体放电模型(HBM) 的冲击电流

• 检查组件布局的ESD 二极管和电阻保护

• 检查ESD MOS/二极管组件是否覆盖了正确的标志层

• 确保保护电路组件正确连接至电源线,且电压范围正确

Calibre® PERC™产品与Calibre 平台的其他产品协同运作,不仅能检测到违反可靠性设计指导原则的情况,还能就电路连通性、拓扑、物理布局和设计规则提供全局的浏览环境,从而帮助设计工程师电路可靠性问题除错。

Mentor Graphics 的Calibre 设计解决方案市场部资深处长Michael Buehler-Garcia 表示:“UMC 和Mentor 已合作开发出了一套自动化解决方案。利用该解决方案,设计工程师可以更轻松地确保实现一流的设计可靠性,同时显著提升设计验证效率。随着汽车、医疗和其他市场对电子技术可靠性及设计开发周期的日益重视,将Calibre® PERC™和Calibre RealTime 并入到您的IC 设计工具箱将为您带来显著优势。”

UMC 计划在未来各个制程的更新发布中增加更多的可靠性检查。

评论