EUV微影技术准备好了吗?

又到了超紫外光(EUV)微影技术的关键时刻了。纵观整个半导体发展蓝图,研究人员在日前举办的IMEC技术论坛(ITF)上针对EUV微影提出了各种大大小小即将出现的挑战。

本文引用地址://m.amcfsurvey.com/article/278355.htm到了下一代的10nm节点,降低每电晶体成本将会变得十分棘手。更具挑战性的是在7nm节点时导入EUV微影。更进一步来看,当扩展到超越5nm节点时可能就需要一种全新的晶片技术了。

目前最迫在眉睫的是中期挑战。如果长久以来一直延迟的EUV微影系统未能在2017年早期就绪的话,7nm制程将会成为一个昂贵的半节点。

不过,研究人员们乐观地看好EUV将会及时准备好,但也预期接下来将出现诸多挑战:

.光源必须至少升级到180W,目前最佳的是ASML展示的110W光源;

.系统必须至少有80%的时间可用,当今系统的可用性约仅50-60%;

.系统必须从每小时70-80片晶圆产出增加到更接近每小时200片晶圆;

.光阻剂必须具有更高感光度,才能以更低剂量与较不粗糙的边缘作业;

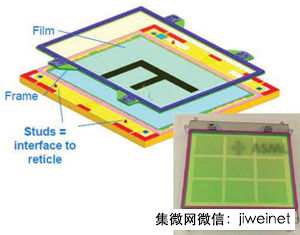

.必须设计新的晶圆保护盖——即薄膜(pellicle),以取代目前ASML提供给客户用于80-110W低功耗级的原始薄膜;

.在查找与修复缺陷方面还需要进一步的改善。

IMEC执行长Luc Van den Hove深信,“EUV可望从7nm节点开始导入制造制程。”IMEC已经为多年来致力于开发EUV系统的先进研究晶圆厂投入高达13亿美元了,目前也已在全球安装的8套最新系统中占有一席之地。

几乎所有的主要晶片制造商都与IMEC合作,针对下一代节点展开前期竞争性研究。今年,东芝(Toshiba)与SanDisk也加入了这一计划。

ASML为EUV客户提供了一种原型薄膜,但可能还得重新设计,才能支援未来发展蓝图所需的更强光源

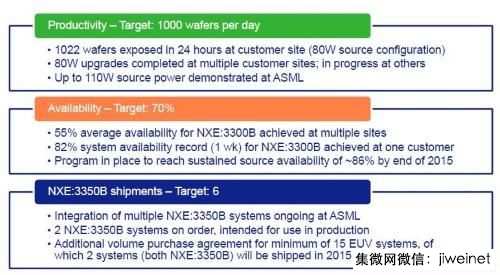

致力于开发EUV的荷兰业者ASML提出了目前的最新进展:一家客户采用其NXE 3300B系统,在一星期中达到了82%的正常运作时间。ASML的目标是在年底前让挥发性光源达到86%的正常运作时间。

这套系统虽然复杂困难,但也至关重要。ASML执行长Peter Wennik强调,“在不断微缩至更小型晶片的制程中,甚至得投入数兆美元。而这是一部结合许多业界工程问题的机器——它让我们得以一个接着一个地解决问题。”

的确,ASML表示每次为重要的光源问题提高功率后,另一个模组就会出现一些问题,因而必须加以升级或重新设计,才能维持系统的正常运转。但IMEC微影技术计划负责人Kurt Ronse表示,“这是一个连续工程的过程。”

少了EUV,7nm也只是半节点

IBM、IMEC、英特尔(Intel)、三星(Samsung)和台积电(TSMC)等业者目前至少都使用了一种最新的EUV系统。至今,大多数的系统也都升级到80W光源了。

然而,ASML的Wennik说:“也许业界还有很多人并不看好EUV,但是从技术角度看来,我们即将实现这项技术。”

事实上,观察人士认为,这一局势将会发生转变。半导体市场分析公司Future Horizons执行长兼首席分析师Malcolm Penn表示:“我们一直在怀疑EUV的能力,但现在看来各种技术汇流将有助于实现最后的目标。”

IMEC制程技术开发资深副总裁An Steegen强调,“业界对于晶圆产出的强劲发展蓝图,让我们有信心EUV将在N7制程时准备就绪。”

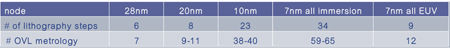

尽管如此,使用的昂贵的EUV系统将受限于每晶片三个关键层。针对7nm制程,EUV系统可在单次实现目前采用浸润式微影需要3至5次才能完成的步骤。

如果少了EUV,在7nm时采用浸润式微影的步骤将大量增加

Steegen预计,目前仍在实验室开发阶段的定向自组装(DSA)技术可望最先用于7nm节点。DSA将有助于减少使用多重图案的需求数量。

如果EUV系统无法在未来的18个月内准备好用于量产,晶片制造商就得在缺少EUV的情况下展开7nm制程。Steegen指出,在这种情况下,7nm或许将成为一种半节点,而不是一项完整的微缩技术。而这对于晶片设计者的限制也将变得更加严格——相较于20nm导入双重图案后的限制而言。

Steegen说:“你可以加大间距以及简化设计,使其变得更有利于微影技术......但有些时候它可能需要五次的曝光。”

总之,晶片显然将会变得比以前更加昂贵。因此,最后可能只有最大型的FPGA和处理器才会利用这种先进制程。利润也将会大幅缩水,大家都得勒紧皮带过日子,许多厂商可能没好日子过了。

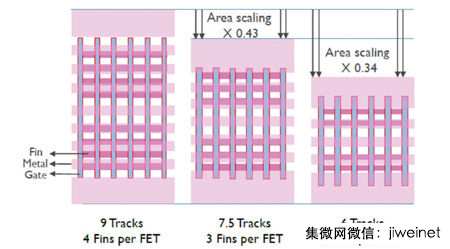

除了微影技术存在巨大的挑战,如何善加利用7nm进行制造也造成激烈辩论。 Steegen认为当今的3D电晶体——鳍式场效应电晶体(FinFET)将让位于新型的环绕式闸极(gate-all-around)奈米线。

此外,像锗这一类具有高迁移率的新材料也很需要。一位分析师预测,英特尔去年开始在10nm时利用锗和砷化镓铟(InGaAs)制造量子阱场效应电晶体(FET)。从EUV、新型电晶体结构和新材料等诸多新元素数量来看,7nm可能会是半导体产业发展史上最困难的制程节点之一。

ASML发布最新的EUV进展

10nm的每闸极成本

尽管最近对于10nm节点的预测乐观,但它的每闸极成本可能无法如预期般地降低。根据IMEC的Steegen表示,10nm将会是第一个需要三重图案以及多达6层光罩的节点,显然会大幅增加最终的开销。

大多数的晶片制造商表示,目前所使用的20nm和14/16nm先进节点,每颗电晶体的成本已经增加了。只有英特尔可说是个例外,该公司宣称其成本在14nm时仍持续降低。市场观察家Handel Jones最近也预测,10nm节点将会比先前的制程世代更具成本效益。

不过,Steegen对此预测持保留态度,“我知道在10nm时的成本将会增加,而且也知道可以有技巧地使其降低,但净成本是否减少、维持现状或提高,则视每家晶圆厂及其设备而异。”

相较于目前为关键层使用双重图案、两次微影步骤的制程,三重图案所需的额外光罩成本将会变得‘十分可观’。因此,巧妙的结合制程与设计技巧将有助于减轻所需的成本负担,但究竟能降低多少成本,目前仍不得而知。

透过金属显影微缩可以提供更大的面积,并降低每电晶体的成本。此外,间距也可能较宽松些,她说。

Wennick宣布,ASML将在今年年底以前推出一款升级的7nm浸润式微影步进机,它能够达到每小时275片晶圆(275w/h)的产出效率,较目前的200w/h更高得多。分析师Penn认为,这将会是有利于减轻10nm成本负担的一大进展。

ASML预计在今年年底前推出7nm浸润式微影系统,可望达到275w/h的晶圆产出效率

EUV技术也可能被加以改造,在因应第二代10nm制程时才及时出现。如果是这样的话,它应该能够用于处理一次或三次曝光图案层,不过该系统也将减缓整体吞吐量。此外,由于该系统十分昂贵,因而是否可真的降低10nm成本将取决于其折旧周期。

“尽管某种程度上已经决定了10nm的未来,但这并不表示无法为其改造EUV工具,”IMEC的Van den Hove说,“我知道有几家公司迫切地想要在10nm时使用EUV。”

好消息是大部份的晶片制造商预计在10nm时制造第二代FinFET,这是一种他们较有经验掌握的电晶体类型。由于英特尔已经展示其14nm的第二代FinFET制程,接下来的鳍片(Fin)将会变得更高且更薄。

更重要的是,Steegen强调,“至今我们所分析的N10制程提供了一个完整的微缩节点。”

IMEC认为,金属显影技术可望大幅减少晶片面积(上图),但却也存在性能缺陷(下图)。

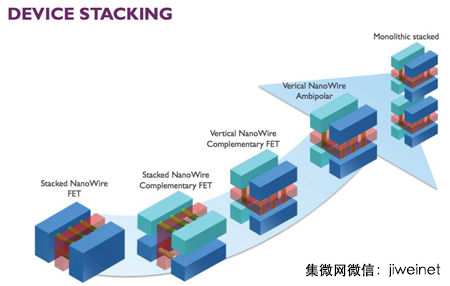

逻辑元件亟需堆叠新方式

事实上,要准确地预测接下来的三个新制程世代(到5nm节点),几乎是不可能的。但有两件事情是相当明确的:未来需要一些新的逻辑电晶体堆叠类型,此外,研究人员们仍能执着地抱持乐观态度。

未来如果无法大幅改造工具,EUV将无法有效使用。对此,ASML表示该公司已经与Carl Zeiss展开合作了。IMEC则展示其于5nm原型研究的初期成果。二者都必须结合使用四重图案浸润以及EUV微影技术。

IMEC掌握了多种堆叠逻辑电晶体的方法,一部份来自于3D NAND的启发

Steegen认为,水平的奈米线未来将会被新的垂直电晶体结构所取代。她说,逻辑元件需要的是类似三星率先突破的3D NAND堆叠进展。

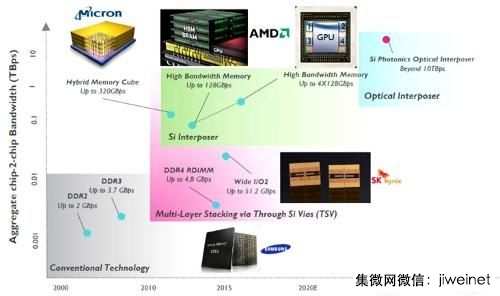

为了打造超高密度的晶片设计,Steegen展示各种堆叠奈米线途径的发展蓝图。她并展示可用于连接堆叠晶片的矽穿孔(TSV)技术进展。此外,她并建议,AMD、美光(Micron)、海力士(SK Hynix)和赛灵思(Xilinx)目前所用的2.5D晶片可望进一步超越现有的矽中介层,从而用于矽光子学。

如今的问题是“如何巧妙地利用3D重新设定像NAND的发展蓝图,”Steegen说。当业界进展到“5nm或甚至3nm时,我们将会发现不同的堆叠架构,让我们能够从那时起重新安排,并且以新的方式开始计算节点。”

“只要市场存在需求,我们就能不断地重新塑造摩尔定律,而其产生的架构并不会像20年前的传统电晶体一样,而是一条持续微缩的道路。”

IMEC认为,矽光子可望在未来的3D晶片堆叠取代矽中介层

评论