高速ADC的电路结构及其速度-精度-功耗之间的权衡

计算机和通信产业的迅猛发展,推动着模数转换器(ADC)在便携式设备方面的应用有了长足进步,ADC的发展趋势像普通模拟集成电路(IC)的发展趋势一样走向高速、高精度和低功耗。对ADC的电路结构设计来说,提高速度,自然要牺牲分辨率和功耗;提高精度或分辨率,要牺牲转换速度和功耗;降低功耗,则要相应降低速度和分辨率。因此ADC的速度-精度-功耗(以下称SAP)三者之间是相互矛盾、相互制约的。在系统应用中,如何选择适当类型和技术指标的ADC,即如何对其SAP之间进行权衡,必须从ADC的电路结构入手。另一方面在对高速ADC的电路进行微电子设计时,如何对其SAP进行权衡又依赖于制造工艺的参数匹配。

本文引用地址://m.amcfsurvey.com/article/3024.htm本文试图从两条不同的技术路线介绍对SAP进行权衡的主要思路,以便对高速ADC的设计与应用有进一步的认识和了解。

如果说ADC的算法是对ADC工作原理的描述,那么ADC的电路结构则是这种算法在硬件上的体现。结构的选择与系统设计密切相关。系统设计的原则是在电路的性能和硬件成本之间进行权衡。

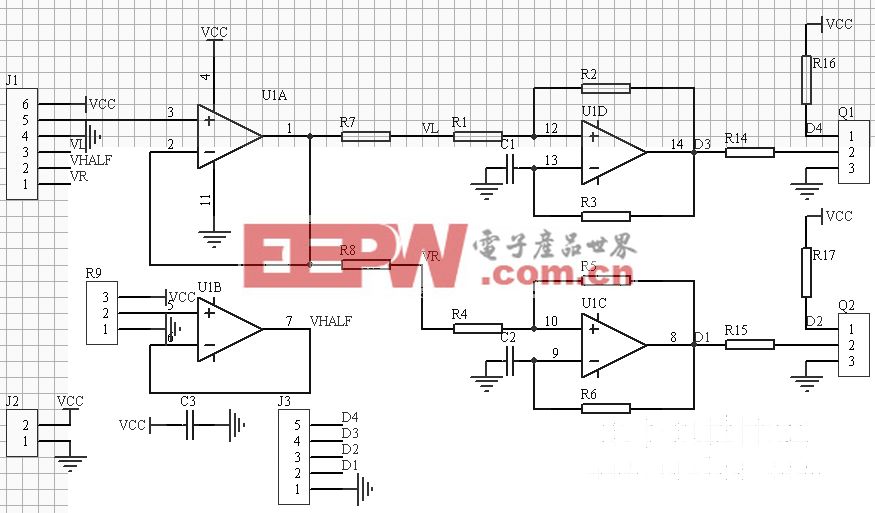

高速ADC(吞吐率大于1MSPS)最典型的结构是闪速型(flash),又称全并行ADC。图1示出了一种N位闪速型ADC的电路结构。

这种结构的主要优点是直接全并行转换,速度最快,因为在一个周期内完成A/D转换。这种结构的缺点是需要2N-1个比较器,导致管芯面积增大和功耗增高,限制集成度的提高。因此仅当分辨率N≤8位,才采用闪速型ADC。

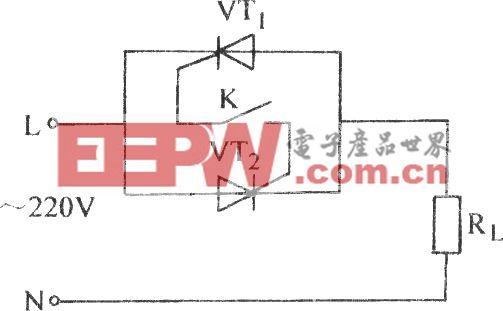

对于N>8位的较高分辨率的高速ADC,对模拟信号采用分步处理的方法,例如折叠或内插型ADC和流水线型ADC,以便克服比较器数目随分辨率呈指数增加的问题。流水线型结构有效地克服了闪速型结构的局限性。它将A/D转换过程分成几级(或几个相继的步骤)来完成。每一级的电路结构如图2所示,它由一个采样保持电路、一个m位ADC(例如一个闪速型ADC)和一个m位数模转换器(DAC)组成。首先,第一级的采样保持电路采集输入的模拟信号。接着m位ADC将采样信号转换成数字量,将此转换结果构成数字输出的最高有效位。再将同一数字输出送给m位DAC,然后从原来的采样信号中减去此DAC输出的模拟量。将这个剩余的模拟量再进行放大送到流水线型ADC的下一级,象第一级一样进行采样和转换。重复这个过程,一直达到分辨率要求的转换级数。从原理上来讲,一个p级流水线型ADC,其中每一级都带有一个m位的闪速型ADC。那么要构成一个N位分辨率的高速ADC(这里N=p×m),则需要使用p×(2m-1)个比较器。例如一个具有8位分辨率的2级流水型ADC,需要30个比较器。对于4级16位ADC仅需要60个比较器。当然,在实际电路设计中还留出几个附加位以便进行误差修正。

在含有相同的比较器数目的情况下,流水线型ADC能达则的分辨率要比闪速型ADC高。这是从1个转换周期增加到p个周期,即以增加总的转换时间为代价换来的。但是由于每一级采样保持器都能保持其输入信号,这样p级转换过程可以同时进行,因此流水线型ADC总的吞吐率应等于一级闪速ADC的吞吐率,即每周期转换一次。但这两种结构ADC的不同之处在于,对流水线型ADC来说,有一个等于p周期的等待时间(latency)问题。流水线型ADC的另一个缺点是,转换过程通常要求一个具有固定周期的时钟。用普通的流水线型ADC对一个变化非常快的非周期模拟信号进行A/D转换会非常困难,因为流水线型ADC通常都按一种周期的速率进行工作。

虽然流水线ADC可以解决较高速度和较高分辨率的应用问题,但功耗问题仍然没有解决。逐次逼近型(SAR)与闪速型可以看作是ADC结构中的两个极端。闪速型ADC使用多个比较器,用一个周期完成A/D转换。而SAR型ADC大家都比较熟悉(在许多电子技术教科书中都有详细的介绍),是用一个比较器在多个周期内完成A/D转换。SAR型ADC能使用一个比较器实现高分辨ADC。但它要达到N位分辨率需要N个比较周期,而流水线型ADC需要p个周期,闪速型ADC需要1个周期,因为逐次逼近型ADC采用了相当简单的电路结构(使用一个SAR,比较器和DAC),所以一直到所有权重都比较完,才能完成一次转换,在N个比较周期内,只能处理一个A/D转换过程。因此,SAR型ADC通常用在高分辨率低速采样场合。SAR型ADC还适合用于非周期模拟信号输入场合,因为转换过程可以随时开始,这个特点使SAR结构非常适合对多个与时间无关的信号进行A/D转换。因为一片SAR型ADC和一片输入多路转换器通常要比N个Σ-ΔADC便宜。当抖动噪声出现时,SAR和流水线型ADC可以采用平均方法提高ADC的有效分辨率。采样速率每提高一倍,有效分辨率改善3dB,或1/2位。

当使用SAR或流水线ADC时应该考虑的一个问题是混叠。对一个信号进行采样的过程会引起混叠——频域内采样信号关于采样频率的镜象。在大多数应用中,混叠效应是不希望出现的,因为这会要求在ADC的前端有一个低通滤波器,以便滤掉高频噪声分量,而使被混叠的信号通过。但是在欠采样中却把混叠效应当作优点来使用,在通信应用场合最常用将一个高频信号转换成一个低频信号。只要信号的总带宽满足奈奎斯特准则(小于采样速率的一半),欠采样是总有效的,而且这种欠采样转换在信号边带中的高频带具有充足的采集量和信号采样性能。快速SAR型ADC具有这种欠采样能力,而速度更快的流水线型ADC在欠采样方面的能力更强。

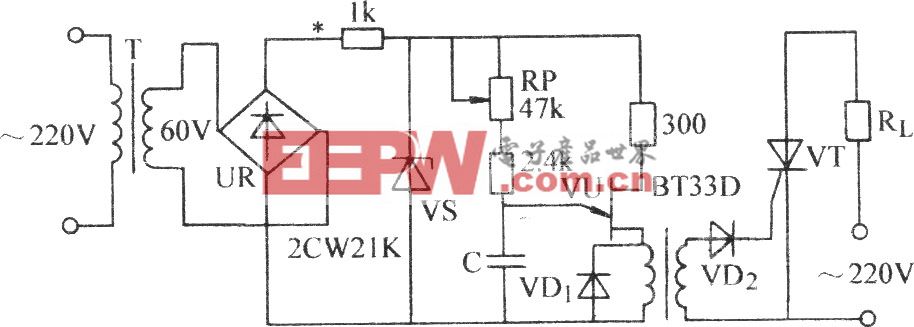

系统设计中选择ADC时,虽然常常考虑到电源要求、接口、封装、工作温度范围等因素,实质上也要对SAP权衡。如果仅从速度和分辨率之间进行权衡(见图3),那么闪速型ADC和Σ-Δ型ADC是两个极端。闪速型对应速度最快、分辨率最低的ADC,而Σ-Δ型对应分辨率最高、速度最低的ADC。关于这几种典型ADC的特性比较见表1和表2。

其中性能等级为“1”表示此结构ADC的该项性能比其它结构ADC好,“2”则次之,以此类推。“*”表示具有表中列出的功能。

其中N为分辨率,p为分级数,比如,半闪速型ADC,p=2。

高速ADC的电路设计对SAP权衡依赖于使用制造工艺的参数匹配。在一块IC上,两个在设计上完全相同的器件,在性能上的差异具有随机性,所以在对其性能仿真的物理参数表现出某种程度的随机性失配,这种失配是由制造工艺的随机性引起的。两个完全相同的CMOS晶体管的失配,用两者之间的阈值电压VT、体因子γ、电流因子β和相互距离之差D的随机变量来表征,对于最小器件尺寸通常大于2mm的制造工艺广泛采用实验方法对这些随机变量做仿真。其参数的标准偏差用下式表示:

其中W为栅极宽度,L为栅极长度,D为相互距离,AVT,SVT为工艺参数。

例如,闪速型ADC正常工作取决于每个比较器检测到的基准电压的精确程度,每个比较器的失调电压是一种独立的随机变量,它取决于所采用的制造工艺的匹配特性,直接影响ADC的微分线性误差(DNL)和积分线性误差(INL)。设计ADC的第一步就是计算失调电压的标准偏差。确保根据某种技术指标(成品率)在很高的概率下进行设计。考虑所有比较器的失调电压都是独立的随机变量,可采用Monte Carlo仿真来计算设计成品率作为失调电压的函数。SAP的基本关系式为:

可从3个方面进行权衡。

·工艺尺度成比例变化对SAP的影响;

·电压尺度对SAP的影响;

·工艺参数对SAP的影响。■

评论