基于MIPS内核的HDTV-SoC平台总线接口模块

中断控制模块

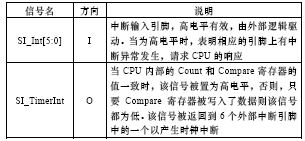

本文引用地址://m.amcfsurvey.com/article/83289.htm中断控制模块负责处理由DeMux、VD、GPIO等外部模块的中断源所发出的中断,对于系统来说,如何使产生的中断尽快得到响应是一个关键的问题。在图1中可以看到MIPS4Kc处理器所提供的中断引脚的连接情况,有关其引脚的说明如表1所示[1]。

表1MIPS4Kc处理器中断引脚描述表

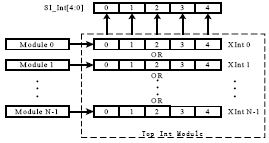

习惯将SI_TimerInt信号接到SI_Int[5]引脚,就像图1中所显示的那样。这样4Kc处理器的外部中断引脚就剩下5根,即SI_Int[4:0]。在本设计中,将系统外部中断分为5级,按照SI_Int[0]到SI_Int[4]的顺序优先级从高到低排列。针对每个外部模块,也将其所有的中断源分为5级,反映到每个模块的输出是一个5比特的寄存器XInt[4:0],同样,按照XInt[0]到XInt[5]的顺序中断优先级从高到低排列。假设系统有N个外部模块,则各个模块输出的XInt之间相或即得到SI_Int的输入,这些逻辑在TopInt模块中实现,如图5所示。

图5 TopInt模块内部逻辑

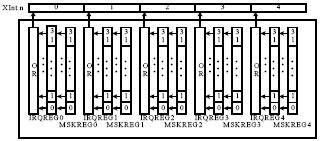

需要说明的是,TopInt模块本身也被当作系统的一个外部模块,系统可以对其进行与其它模块相同的寄存器读写操作。这样CPU在处理外部中断时,就可以通过读取XIntn寄存器的内容,追溯中断的产生源。另外,在每一个外部模块内部,设置5个32位的中断请求寄存器IRQREG0~IRQREG4和5个32位的中断屏蔽寄存器MSKREG0~MSKREG4。当MSKREGn寄存器中的某个比特位被置“1”时,则IRQREGn寄存器中相应比特位的中断被屏蔽。在每一个IRQREGn寄存器当中,32个比特位之间相或即得到该模块相应XInt寄存器中的第n比特位的值。由此也可以看出,按照IRQREG0到IRQREG4的顺序,中断优先级从高到低。它们之间的逻辑关系如图6所示。

图6 外部模块中断寄存器逻辑关系

另外,为了便于CPU的访问,所有这些寄存器在模块中都有编址。这样对于任意一个中断,最多通过两次查询CPU就可以获知产生该中断的中断源。

仿真与综合

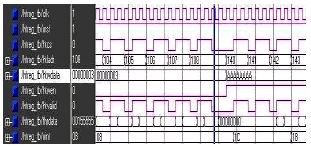

设计的仿真工作是分两部分进行的。各模块先单独仿真,待波形正确后再各模块联调。在编制TESTBENCH时,分别在不同的文件当中处理不同的工作情况。具体到HIF模块,仿真主要完成如下方面的验证:寄存器的写入和读取、双口RAM的写入和读取以及中断的产生和获取。在设计中,采用VHDL语言编写代码,以及Mentor公司的ModelSimSE5.7工具进行编译和仿真。在仿真时,SMIC库提供的双口RAM模型作为外部模块挂接在系统中,模型的接口时序与图4中所示的完全一致。图7为节选的HIF模块仿真波形。

图7 HIF模块仿真波形图

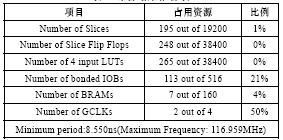

由于整个SoC系统的设计工作尚处于FPGA验证阶段,因此在综合时选用Xilinx公司的ISE6.1软件中自带的XST综合工具,FPGA器件选择Virtex-E系列的XCV2000E。综合后的结果报告如表2所示。

表2 综合结果报告表

总结

由仿真和综合的实验结果可以看出,HIF模块的设计可以满足系统在功能上的要求,而且综合后的模块所占用的FPGA的面积和资源的比例都很小,有些甚至可以忽略不计,因而不会影响到系统中其它模块的设计与实现。而综合后的主工作频率为116.959MHz,完全满足设计要求。

评论