Rambus联合金士顿开发出“线程式内存条技术”

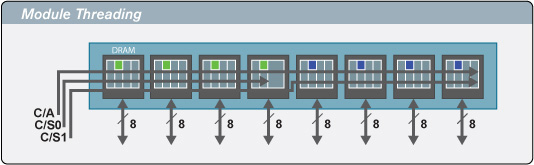

Rambus公司以往的新闻几乎都与XDRDRAM的官司有关,不过这次他们则和金士顿合作开发出了一种可用于增大DDR3内存带宽的技术“线程式内存条技术”(Threaded memory module)。这种技术基于现有的DDR3技术,不过将内存条上的内存芯片进行了分块处理,位于各个分块内部的芯片共享一个命令/地址端口,不过数据传 输部分则可通过各自独立的传输通道进行传输,传输的位宽可达64字节(512bit),这样就可以将传统DDR3内存的带宽提升50%左右,而且采用这种 技术之后,内存芯片的活跃时间也比过去降低了一半,如此便可节省20%的能耗。

本文引用地址://m.amcfsurvey.com/article/98387.htm

目前单通道DDR3内存的位宽为64bit,双通道配置则为128bit;而线程式内存条技术则只需单通道便可提供512bit的数据传输位宽,这样理论峰值带宽便大大提高了,不过按Rambus公司自己提供的实测数据表明,实际的数据传输带宽增加幅度一般在50%以下。

两家公司将在Intel IDF2009论坛上展示采用这种技术的实际产品。

评论