基于FPGA的远程图像采集系统设计

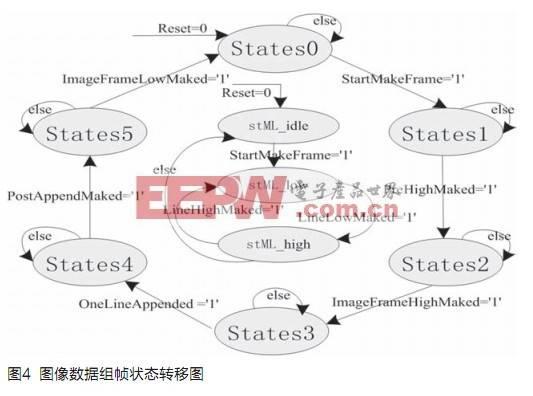

状态机在FPGA内部设计成两部分,为组帧状态机(外圈)和组行状态机(内圈)。其中组帧状态机各状态转移顺序及条件见图4,各状态占用时间可以通过组行状态机中的行计数来控制,近而可以完成不同大小规格的图像的接收。组帧状态机共有6个状态。

state0:空闲状态(系统复位)。state1:帧有效期开始到行有效期开始之间的延时。state2:图像帧有效期,state3:图像参数帧有效期。state4:行有效期结束到帧有效期结束之间的延时。state5:帧无效期。Reset为输入的状态机复位信号,在系统复位状态,如果用来启动状态机的信号StartMakeFrame = 1,状态机开始工作,进入系统下一状态,组帧状态机在各状态转移条件满足时,依次进入下一状态,否则,保持在原状态。

组行状态机共有3个状态。

stML_Idle:空闲状态。stML_High:行有效期。stML_Low:行无效期。在外圈组帧状态机的每个状态中,包含n个组行状态,所包含的组行状态机中的行数即组帧状态机各状态所占用时间,组行状态机和组帧状态机启动条件一致,同时启动。

评论