基于FPGA的远程图像采集系统设计

以采集可见光图像数据为例,上电复位期间 系统处于states0状态,状态机用外部输入的7.375MHz时钟同步整个运行过程,图像的帧、行、图像数据等信号在同步时钟的下降沿跳变,上升沿锁存。一帧图像数据的大小为512×512bit,并将图像附带的参数信息写入图像数据后一行(即513行),在帧有效期间(states1、states2、 states3状态),CLK 信号作为行计数器的时钟,每帧图像在行有效之前有1行无效图像信号(states1), 在states2状态下,控制采集一帧中的前512行,在states3状态下,采集图象的参数信息,将图像数据和状态参数组合为统一的数据帧,采集完一帧图像数据后等待下一个帧同步信号的到来。在行有效期(stML_High)控制采集一行中的512个像素点数据,在CLK信号的上升沿进行计数, 在数据有效期间采集完512个像素点,等待下一个行同步信号的到来,按同样方式对下一行512像素点数据进行采集,直至采集完一帧中的512行。

本文引用地址://m.amcfsurvey.com/article/99680.htm系统仿真

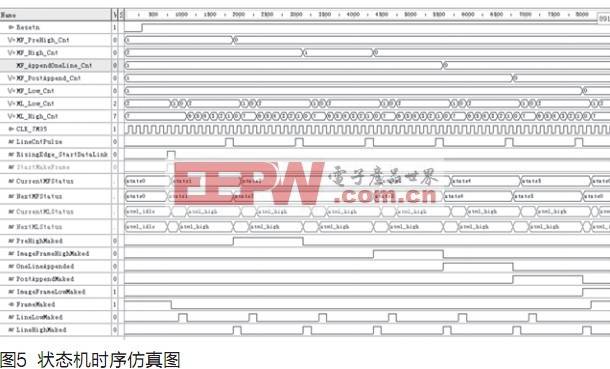

在该系统中,状态机设计是难点,图5是运用Active-HDL7.1仿真工具的状态机仿真结果,仿真时,采用7.375MHz时钟同步,状态机启动后,计数寄存器里的数据递减,进而产生各状态转移满足的条件,以此实现状态机的翻转。

在Active-HDL7.1中编写TestBench文件时,通过向组帧状态机计数寄存器写数,来控制各状态所占用的时间,利用 StartMakeFrame信号高电平启动状态机,各状态发生翻转时,状态完成标志就产生产生高电平跳变。

根据图5的仿真结果,可以看出组帧状态机工作正常,所有的逻辑关系也都验证无误。

评论