关于DDR的电源设计部分,你值得收藏!

通常来说在DDR硬件电路设计过程中,关于DDR的电源设计部分存在着不合理的部分,下面简单介绍一下DDR的电源:

DDR的电源可以分为三类:

(1)主电源VDD和VDDQ

主电源的要求是VDDQ=VDD,VDDQ 是给IO buffer供电的电源,VDD 是给但是一般的使用中都是把VDDQ和VDD 合成一个电源使用。有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

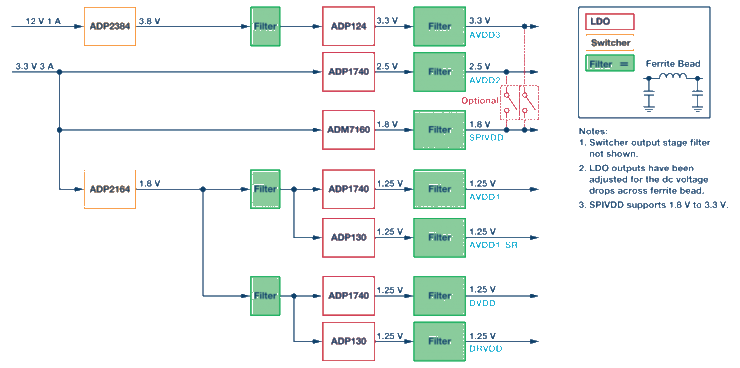

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR 的电流一般都比较大,所以PCB 设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个10nF~100nF的小电容滤波。

(2)参考电源Vref

Vref 为参考电压,要求精准恒定,用于判断信号高低电平的依据。

所有的DDR信号其实都是差分信号,其都是相对于Vref的,所以也都是差分信号,更详细的内容参见“高速电路设计实践”中关于DDR的章节。

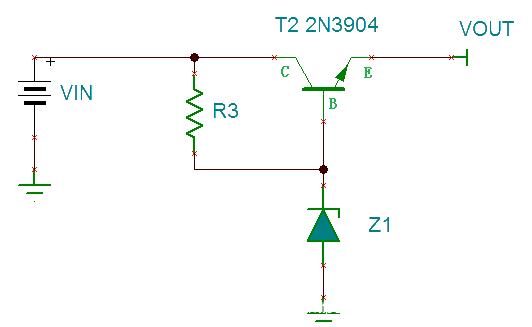

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA 的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的电容滤波,并且每个分压电阻上也并联一个电容较好。

Vref又分为Vrefca和Vrefdq:

Vrefca Supply Reference voltage for control, command, and address: Vrefca must be

maintained at all times (including self refresh) for proper device operation.

Vrefdq Supply Reference voltage for data: Vrefdq must be maintained at all times (excluding self

refresh) for proper device operation.

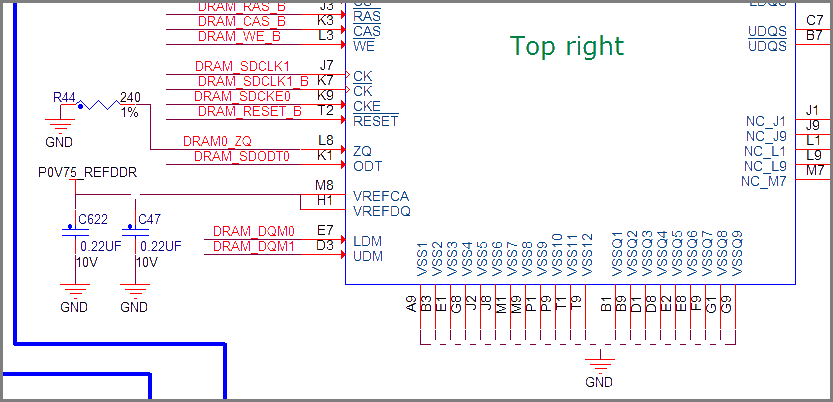

下面是FSL i.MX6设计截图:

Maintain at least a 20–25 mil clearance from V REF to other traces; if possible, isolate VREF with adjacent

ground traces.(nxp-fsl设计指导书)

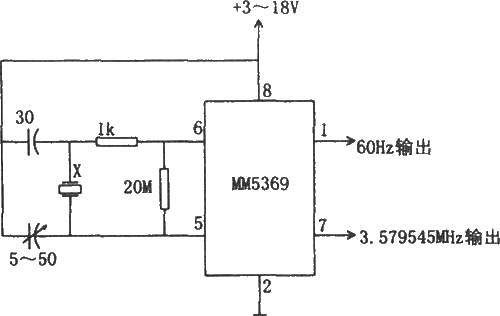

(3)用于匹配的电压VTT(Tracking Termination Voltage)

VTT,用于上下拉电阻的电源,电流大,波动大,噪声也大。

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR 的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT 的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源即可以提供电流,又可以灌电流(吸电流)。

一般情况下可以使用专门为DDR 设计的产生VTT 的电源芯片来满足要求(曾经使用过程中用了简单的线性稳压器也没发现出现什么问题,这种方式还是不建议的!)。

而且,每个拉到VTT 的电阻旁一般放一个10nF~100nF的电容,整个VTT 电路上需要有uF级大电容进行储能。

一般情况下, DDR 的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质 量。而地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T 点的结构,所以常常需要使用VTT 进行 信号质量 的匹配控制。

评论