基于IEEE 1588的同步以太网应用解决方案

3 应用实例

3.1 Si5315芯片

在实际应用中,采用Silicon Labs公司生产的Si5315芯片。该芯片为一款抖动衰减时钟倍频芯片,采用8 kHz~*.53 MHz的双时钟输入,并且产生2个独立的倍频时钟。在同步方面,主要采用Silicon Labs的第三代DSPLL技术,能够产生任意比率的频率合成以及在高速率下的去抖动。除支持SONET/SDH和以太网时钟外,Si5315还可支持10G线路编码率的同步以太网时钟倍频芯片。

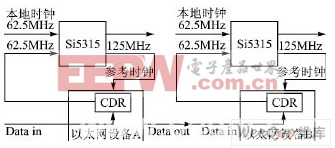

具体应用实例如图3所示。本地时钟输入62.5 MHz作为芯片的一路输入,经过Si5315倍频后输出端口一路为125 MHz。将其信号引入以太网设备的CDR模块(数据时钟恢复模块)作为参考时钟。当数据进入CDR后恢复出一个接近62.5 MHz的时钟,再次输入Si5315,经过DPLL锁相达到芯片认为符合要求的时钟后,本地时钟的输入被屏蔽。当网络中所有的设备都完成此项操作后,整个网络的时钟同步完成。在具体的应用中前级的数据时钟往往抖动十分严重,经过Si5315芯片处理后,时钟能恢复得很好,并且所有设备的时钟都保持了一致性。

图3 Si5315同步芯片应用实例

3.2 DP83640芯片

IEEE 1588的精密时钟协议(PTP)能够实现高精度的以太网时间同步,但是如果需要达到ns级的时钟同步性能,仅仅通过软件是很难实现的。因为在线路上接收PTP包之后,对它们进行处理的每一种器件都会增加同步误差。DP83640通过在物理层以硬件加软件的方式使得ns级的时钟同步成为可能。

DP83640是一款基于IEEE 1588标准的时钟同步芯片,采用硬件和软件结合的方式提供最高的精确度实时工业的时钟同步,可确保分布式上各节点能按照主机时钟的时间同步定时,并确保各节点之间的时间偏差不会超过8 ns。一旦线路上有PTP包,即被DP83640的精密PHYTER所读取。

DP83640具有几个内部时钟,包括本地参考时钟、1个以太网接收时钟和1个PTP时钟信号源;同时,还包括1个内部的PTP数字计数器,以及可以控制数字计数器和PTP时钟速率(频率)的逻辑。

在同步以太网交换机的方案中,通过替换以太网层并增加IEEE 1588 PTP软件实现。如图4所示,CPU、交换芯片和DP83640通过MII口连接起来组成一个系统。交换机成为以太网中同步的一个器件,使得交换机所形成的以太网及该网络下所挂的器件都满足IEEE 1588协议,最终形成同步以太网。

图4 基于DP83640的同步以太网交换机应用框图

结语

从目前的原型实验和应用来看,IEEE 1588中标准化的精确时间协议可以达到亚微秒级的同步精度,并且有可能达到更高的精度。IEEE 1588为基于多播技术的标准以太网的实时应用提供了有效的解决方案,但同时也存在一些尚待进一步研究的问题,如主时钟的容错性能、振荡器的稳定性对时钟的影响等。相信今后该标准会更加完善,也会有更多的具体应用可以参考。

评论