三线制同步串行通信控制器接口设计

数据接收流程:在帧同步脉冲信号触发下,串行数据在时钟信号rclk上升沿到来时保持稳定,并通过rdata信号线进入数据接收模块。在该模块内部,串行数据经过串/并变换,接收FIFO作为数据缓冲器,将接收到的数据锁存在VHDL程序指定的两个地址寄存器中,一个地址单元存储数据的高八位,另外一个地址单元存储数据的低八位,当数据存满这两个地址单元后,接口向系统发出一个“接收缓存满”的接收中断标志int,系统微处理器响应后,数据被全部取出,并行数据被送往系统的数据总线上,重复进行相同操作,直至连续接收完所有数据,数据接收过程结束。

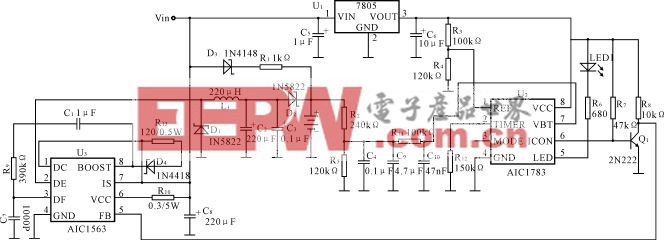

数据发送模块也是三线制同步串行通信接口进行数据发送的核心部分,其模块结构如图6所示。本文引用地址://m.amcfsurvey.com/article/157776.htm

数据发送流程:在sgate帧同步脉冲信号触发下,系统数据总线上的并行数据在时钟信号sclk上升沿到来时保持稳定,并通过数据发送模块开始数据发送。在模块内部,首先发送FIFO数据缓冲器,当并行数据存满该缓存单元后,数据发送模块向系统发出一个“发送缓存满”的发送中断标志int,系统微处理器响应后,并行数据从发送FIFO内读出,经过并/串变换成串行数据,最高位MSB最前,最低位LSB最后,并被送往发送数据信号线Sdata上,发送至外围设备接口,重复进行相同操作,直至发送完毕所有数据,数据发送过程结束。

3 结 语

本文在介绍了三线制同步串行通信机制基础上,首先对三线制同步串行通信接口进行了硬件电路设计,然后针对传统电路设计方式的不足,构建了基于CPLD/FPGA的三线制同步串行通信控制器接口结构,详述了各个功能模块及其工作原理,设计合理,并且满足了实际应用要求。目前,此接口结构模块已作为FPGA设计中的关键子模块被成功应用于某航天项目及其配套的硬件测试平台中。

评论