高可靠性微控制器设计研究

2.2 纠错检错(EDAC)

2.2.1 EDAC概述

EDAC可以用来检测电子设备中由SEU引起的存储为翻转错误。EDAC的基本结构包括3个部分:编码模块,解码模块,存储模块。其中EDAC 编码模块将需要处理的数据进行相关算法的编码,产生校验码,与待处理数据一同存入存储模块。数据需要读出的时候,EDAC解码模块将数据与相应校验码进行解码处理,得出正确结构。编码与解码所采用的编码方式可以根据需要选择,如汉明码,最佳奇权码,藤原英二码等等。

2.2.2 汉明码介绍

下面以扩展汉明码为例说明编码纠错检错的原理。 扩展汉明码(Extended Hamming Code)在存储系统的纠错检错中得到了广泛应用。他的最小码距是4,对于数据位数 k,校验位数 r,他们之间的关系需满足 2r-1 ≥ k+r。如果数据位 k增加一倍,校验位 r也只需要增加1位,所以它具有相当高的编码效率。 8位数据经过4位编码后的数据结构如下:

C= [D7D6D5D4D3D2D1D0C3C2C1C0]其中 D7~D0是数据位,C3~C0是校验位:

C3= D7 D6 D5 D4 ; C2= D7 D3 D2 D1; C1= D6 D5 D3 D2 D0 ; C0= D6 D4 D3 D1 D0

解码时需计算存储数据的伴随向量 S: S3= C3 CB3;S2= C2 CB2 ;S1= C1CB1;S0= C0 CB0 其中 CB0,CB1,CB2,CB3为 8位数据在解码时刻的校验位。根据算得的伴随向量 S我们就可以判断数据位是否发生错误及错误发生的位置。

2.3 两种纠错方法的比较

TMR与 EDAC都属于硬件冗余,对于不同字长的存储器,他们所占用的面积开销和时间开销是不同的。TMR所占用的面积开销包括冗余的2个目标器件以及判决器及附属电路逻辑,EDAC所增加的面积开销则包括了增加的校验位,编码器,解码器及附属逻辑 1。根据以上分析我们可以得出结论,对于保护寄存器,寄存器组等容量较小的存储器件,TMR有实现简单,增加面积较少的有点。而对于大容量的存储器,则应当采用 EDAC来进行纠错检错。

3高可靠性8051具体方案设计及实现通过对 SEU的机理分析及 mc8051结构分析可以得出,容易受到粒子辐射的关键部位有

3:特殊寄存器(Special Function Register ,SFR),内部 ram,外部 ram。本论文就上述三个模块对 mc8051IP核进行了该进。

3.1特殊寄存器(SFR)

mc8051IP核的特殊寄存器(SFR)均在 control_mem文件中实现。该模块实现 8051译码功能。SFR字节地址范围是80H-FFH,他们在 RAM中并不是完全连续的,21个 SFR离散的分布在上述字节区域的128个字节单元中。在mc8051IP核中并没用将这些SFR设计在内部 ram中,而是对应地址分别实现的。对 SFR的加固处理是采用了 TMR技术。具体实现步骤如下:

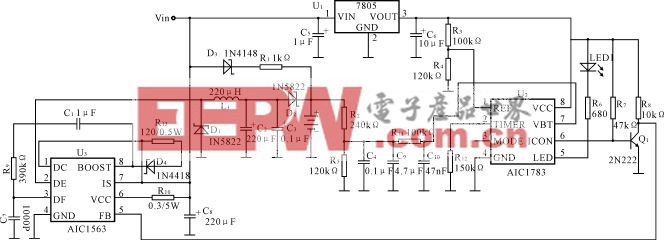

综合后结果截取如下图:

评论