高可靠性微控制器设计研究

3.2内部 RAM本文引用地址://m.amcfsurvey.com/article/163360.htm

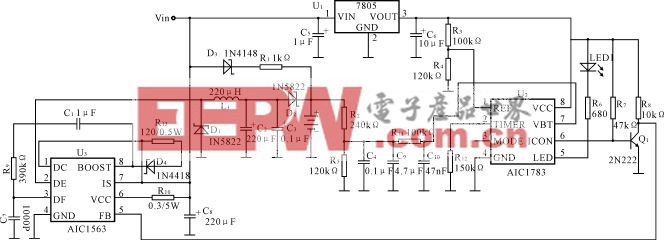

该 IP核可支持 128字节内部RAM.由 2.3分析,方案采用 TMR方式对内部 RAM进行处理,选用 3个相同的 128字节的 RAM作为冗余的存储器,由 mc8051_ram_fsm与 mc8051_ram_dataflow两个模块组成了内部 RAM的数据通路,其中前者完成写优先的读写状态控制,后者完成数据流向控制。数据通路负责完成数据校验。控制通路与数据通路组成内部 RAM接口逻辑。经过仿真后内部 RAM接口结构框图及读写时序如下:

图 2(B)可看出:写数据时,数据输入后第二个周期被写入RAM;读数据时,读指令被检测到后的第 5个周期经校验后的正确数据被输出并且被回写给RAM。在接入工程应用时需将外部时钟进行 6倍频以配合 cpu读写时序。

3.3 外部 RAM

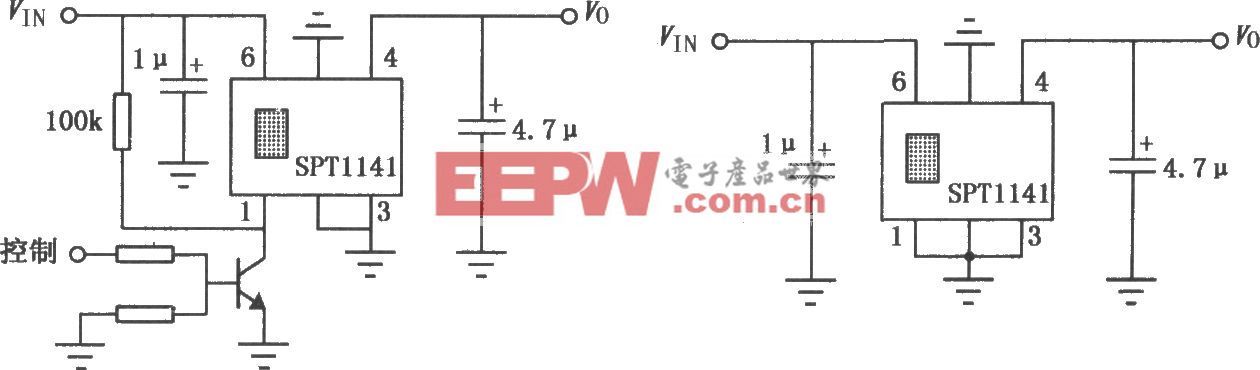

外部 RAM最大可以支持64K,同样由 2.3分析,方案选取能纠 1位错检 2位错的扩展汉明码进行 EDAC处理。其中,数据处理单元完成数据的编码,解码,地址锁存及数据输出功能。读写状态机 FSM完成外部 RAM的读写状态控制,同样,为配合 ram的 IP软核时序,我们将 FSM设计为写优先。仿真后的 EDAC结构框图及读写时序如下:

需要指明的时上图仿真时外部时钟为 10Mhz,经过 altera公司 alt_pll进行了 6倍频及相位调整,前一个写指令未被执行的原因是 PLL需要 2到 3个时钟周期的调整稳定频率输出。 EDAC模块的读写时序与内部 RAM相似,写数据时第 2个时钟周期经过处理后的 8位原数据以及 4位校验数据一同被写进 RAM,读数据时,读出的 12位数据经过解码纠正后在第 5个时钟周期输出 8位数据并将纠正后的 12位数据回写进 RAM,以防止 SEE的积累。由时序图可知以上设计完全符合设计要求。

3.4全系统仿真

在完成上述几个方面的 IP定修改之后,对 mc8051的顶层系统进行了 modelsim的综合前仿真,仿真部分结果如下:

仿真时将 ROM的初始化文件设置为 mc8051文档中的 tc1.hex,方便与原 IP核进行对照。为在 modelsim仿真前,我们已将 altera的 altera_mf库加入到 modelsim库文件中。在进行功能仿真的时候调用了其中的 alt_pll来进行时钟处理。在使用该 IP核时可以根据具体采用的器件来完成倍频的功能。以上时序完全正确,说明修改后的 IP核与原 IP核功能上等同。

4结论

本文在oreganosystems公司提供的开源mc8051IP软核的基础上根据高可靠性航天电子设计的方法修改了部分模块,实践证明修改后的功能与原 mc8051IP 核完全相同,达到设计目的。可以根据需要将 IP核综合后生成的网表文件下载进现场可编程逻辑器件( FPGA)或者进行流片设计成 ASIC,具备航天使用价值。本文创新点:本文根据在研航天项目需要,定制了一种可适应航天工作环境的微控制器IP核。采用常用的容错技术对普通商用 IP核进行了加固。该 IP核的成功改造,可以一定程度上减轻我国军品级芯片对国外的依赖,提高了效率,为后续的研究积累了宝贵经验。

评论