基于FPGA的DDS基本信号发生器的设计

由以上代码生成的.mif文件即可存E盘目录下找到,将.mif文件加载到ROM中,实现对ROM的初始化。

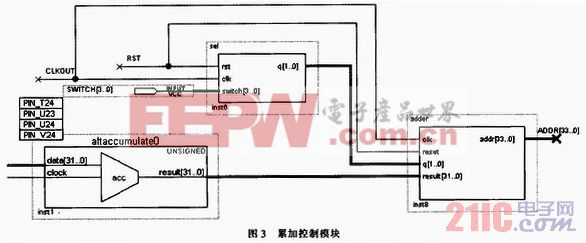

3.2 累加控制模块

累加控制模块如图3所示,为了实现波形选择性输出,本设计在累加控制部分增加了选择器,即图3的sel模块,作为系统寻址地址的高两位,实现对波形查找表的范围选择功能。累加器Altaccumulate0的输出做为累加控制模块的低32位的输出,实现在指定范围内对查找表进行寻址。此设计方法相当于做了一个多路数据选择器。四位拨扭开关作为sel模块的输入控制,将寻址地址转换成所需波形首地址,即可实现对波形选择的控制。Adder模块将sel和Altaccumulate0模块输出进行位拼接运算。其部分代码如下:

always@(posedge clk)

begin

addr={q,32’b0}+{2’b0,result};

end

设计中为了节省ROM的容量而采用相位截断的方法,取累加器输出的高十位作为ROM的寻址地址来进行查表。本文引用地址://m.amcfsurvey.com/article/189967.htm

评论