基于FPGA的DDS基本信号发生器的设计

3.3 LCD 12864口核设计

对于Altera SOPC Builder未提供的一些外设接口模块,用户可以通过自定义逻辑方法在SOPC设计中添加自己开发的IP核,通过Avalon的读写时序对各个设备进行操作。本设计通过构建IP核来直接控制NiosⅡ和LCD12864的接口,按照指定的时序将波形参数显示在LCD上。在SOPC Builder中自己定义component,并把液晶显示模块看成外部存储器,直接做成Avalon总线Slave设备,IP核设计包含软件部分和硬件部分,需要写HDL模块,定义控制状态、数据寄存器和控制位,描述组件与Avalon总线的接口以及组件与液晶屏的接口。系统编辑器从文件中读取I/O信号和参数信息。其次对LCD模块进行初始化,由于SOPC Builder中的LCD12864控制模块已经考虑了LCD的读写时序,所以使用NIOSⅡ IDE进行LCD驱动和控制时只需对LCD进行初始化。

3.4 NiosⅡ嵌入式处理器系统

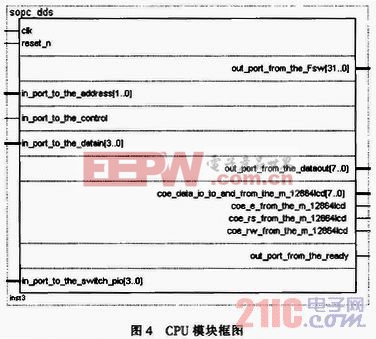

NiosⅡ是Altera针对其FPGA设计的嵌入式软核处理器,它与其他IP核可构成SOPC系统的主要部分。它具有灵活的自定义指令集和自定义硬件加速单元,以及图形化开发环境NiosⅡIDE。经由SOPC Builder生成NiosⅡ嵌入式处理器系统,其CPU模块框图如图4所示。本文引用地址://m.amcfsurvey.com/article/189967.htm

利用NIOSⅡIDE开发工具完成所有软件开发任务,系统接收拨扭开关扫描模块发来的4位扫描码,根据扫描码数值的不同进入不同的子程序,然后再通过FPGA的键盘扫描模块向NIOSⅡ处理器发送键盘扫描码,软核处理器根据接收到的扫描码产生相应的信号数据以及控制信号,并通过PIO传送给FPGA中的DDS模块,实现频率控制字的变化,即输出频率可调,并将信号数据显示在LCD上。同时DAC器件将DDS产生的8位信号数据进行数模转换,从而产生频率可调的方波、三角波、正弦波、锯齿波。

4 结束语

该信号源能够很好地满足对不同波形、不同频率的信号的需求,具有很强的实用性,并且可以方便地通过液晶显示器直观地观察到波形信号的参数信息。由FPGA实现的DDS信号发生器不仅可实现频率可调波形变换且具有频率切换快,信号的质量和精度高于模拟方式的特点。

评论