FPGA控制下面阵CCD时序发生器设计及硬件实现

2.2 驱动时序分析

ICX098BQ芯片的一个工作周期分为4个阶段:感光阶段、垂直转移阶段、帧转移阶段和水平读出阶段。感光阶段进行光电转换,完成感光阵列的电荷积累。垂直转移阶段实现感光阵列积累的电荷包读出转移到相邻的垂直移位寄存器。帧转移和水平读出阶段包括电荷包从垂直移位寄存器向水平移位寄存器并行转移以及从水平移位寄存器向输出放大器的串行输出。

在CCD工作周期中,首先在Vφ1、Vφ2A、Vφ2B、Vφ3的控制下,感光阵列的垂直移位寄存器进行一次电荷转移,将之前残留下来的电荷彻底清除,为下一步做好准备。然后垂直驱动时钟V1将持续一段高电平。此刻,读出时钟V2A、V2B跳变为+15 V的高电平窄脉冲,读出时钟迅速将感光阵列中的所有像素电荷并行地转移到相邻的垂直移位寄存器中。在每个行消隐期间,垂直移位寄存器中的电荷在四相垂直驱动时钟Vφ1、Vφ2A、Vφ2B、Vφ3交替作用下逐行地向水平寄存器转移。此时水平驱动时钟Hφ、Hφ2保持不变。在行正程期间,转移到水平寄存器的一行信号电荷受频率为10 MHz的两相水平驱动时钟Hφ1、Hφ2控制,向浮置扩散放大器水平转移。输出放大器以复位门时钟RG的频率将像素电荷逐一转换成信号电压后串行输出,在输出端得到与光学图像对应的一行的视频信号。

3 基于VHDL的时序发生器设计

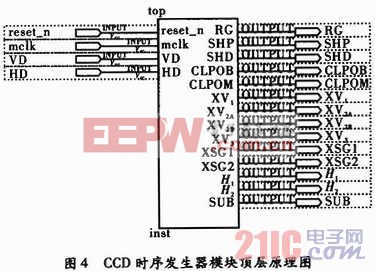

由于面阵CCD驱动时序的复杂性,选用硬件描述语言VHDL设计CCD时序。VHDL采用自顶向下的设计方式,具有较强的硬件描述能力和仿真能力。在程序中,定义的输入输出端包括两个输入端和10个输出端。

整个驱动时序发生器的实现程序为两重嵌套的循环,整个过程采用3段式状态机来完成。一个CCD工作周期流程如下:

(1)对水平寄存器进行清空复位。

(2)垂直转移,将电荷从感光区转移到相邻的垂直移位寄存器。

(3)进行帧转移和水平读出阶段。帧转移一行,水平读出一行,直到整帧读出完毕。

(4)返回,读取下一帧。即返回步骤(1)。

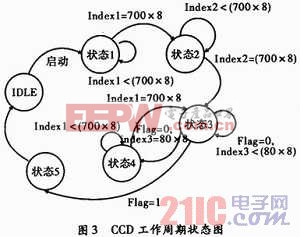

状态转移图如图3所示。本文引用地址://m.amcfsurvey.com/article/191097.htm

IDLE:为空闲状态;当积分启动后,转到状态1。

状态1:为预读出状态;读出水平寄存器内的电荷,当水平读出700个电荷后,转向状态2,否则,自循环。

状态2:为垂直转移状态;使感光区的电荷转移到垂直移位寄存器,垂直转移后,转到状态3。

状态3:帧转移状态;其中Flag为场有效标志,当Flag=1时,进入积分状态,开始下一帧的工作。

状态4:水平读出状态。

状态5:积分状态,转向空闲状态,开始下一帧的工作。

根据分析,设计出产生上述时序的顶层原理图,如图4所示。

评论