FPGA控制下面阵CCD时序发生器设计及硬件实现

LT3487是一款单芯片稳压器,可以在单输入电压(2.3~16 V)基础上,获得正负电压。与其他同类型稳压器相比,其输出断开功能可避免在器件关闭期间出现直流漏电所导致的功率损耗。文中输入电压值为+5 V,通过USB接口从电脑得到,其供电能力完全能够满足驱动及CCD电路的电流消耗。

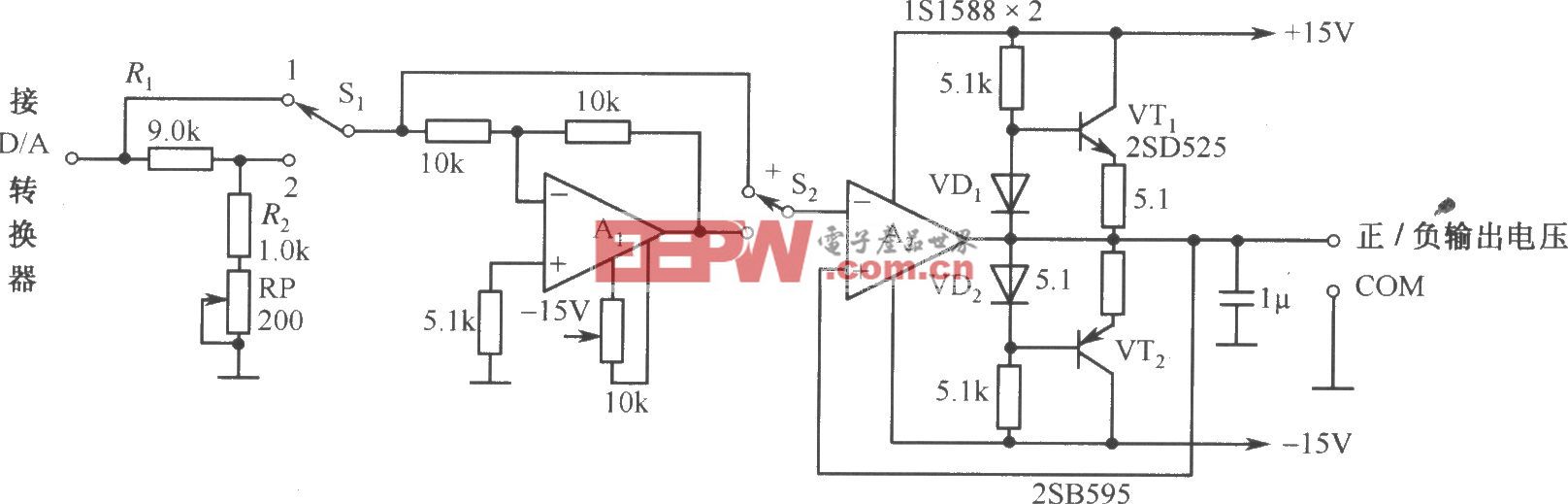

4.2 驱动器电路

如图7所示,CCD工作所需的驱动时序均由CycloneII系列器件EP2C8T144C8N产生。在CCD工作所需的4路垂直驱动时钟Vφ1、Vφ3、Vφ2A、Vφ2B中,Vφ1、Vφ3为两电平,Vφ2A、Vφ2B为三电平。而FPGA产生的信号只有‘0’和‘1’两种状态。对此,可将时序发生器中的XV2和XV3时序分别与XSG1和XSG2时序利用脉冲合成驱动器CXD1267AN进行合成来生成Vφ2A、Vφ2B。本文引用地址://m.amcfsurvey.com/article/191097.htm

如图7所示,在FPGA产生的时序发生器的10路信号中,XV1、XV2、XSG1、XV3、XSG2、XV4经过脉冲合成驱动器CXD1267AN后,合成为Vφ1、Vφ2A、Vφ2B、Vφ3;而H1、H2和复位脉冲RR通过ACT04反相器后进入CCD进行工作,提升了H1、H2和RG的驱动电压,增加了CCD的水平读出能力。驱动电路在-5.5 V和+15 V的电压下工作。在电压偏置电路和驱动电路的工作下,产生的CCD信号为包含直流分量大小为几百mV的交流信号。

4.3 硬件测试结果

物体的图像经过光学镜头投射到面阵CCD上,并将上文实现的驱动时序用于面阵CCD的驱动,并用示波器对隔直后的CCD信号进行测量。

图8为CCD输出的某一行中各感光像元电荷信号的波形,每个周期代表一个像元。每个像素单元分为3部分,它们分别是复位脉冲馈入、参考电平和数据电平。每个周期中的尖峰为复位脉冲馈入到CCD的读出电容,在CCD输出波形中形成,每个像素感受到光信号的有效值由参考电平和数据电平的差表示。由此可见,在驱动时序作用下面阵CCD能正常工作。

5 结束语

时序控制方案采用VHDL语言进行设计,用EDA软件对所设计的驱动电路进行了仿真。仿真结果表明,该驱动电路能够满足面阵CCD驱动时序的求。

评论