基于高速A/D转换器的视频数据采集系统

2 系统硬件设计

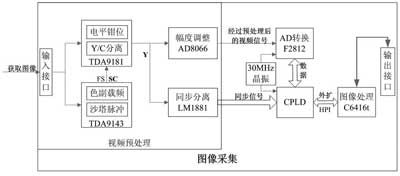

视频采集系统一场图像时间内的采集数据量决定了成像质量,也就是常说的分辨率或者叫像素。按照我国PAL制式的信号特点,每秒扫描25帧图像,每一帧图像又分奇偶两场,那么,一场图像的扫描时间就是20 ms。目前市场上的摄像头,不管是CCD或是CMOS成像的,纵向分辨率基本都在400线的以上。因此推得单行视频信号的持续时间小于20 ms/400=50μs左右。那么,如何在50μs内对视频信号进行快速地A/D转换,得到更多的灰度值数据,以提高横向分辨率就成为视频采集系统设计的关键问题。

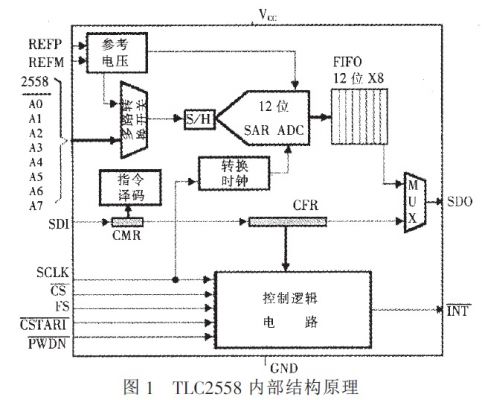

2.1 高速A/D转换器

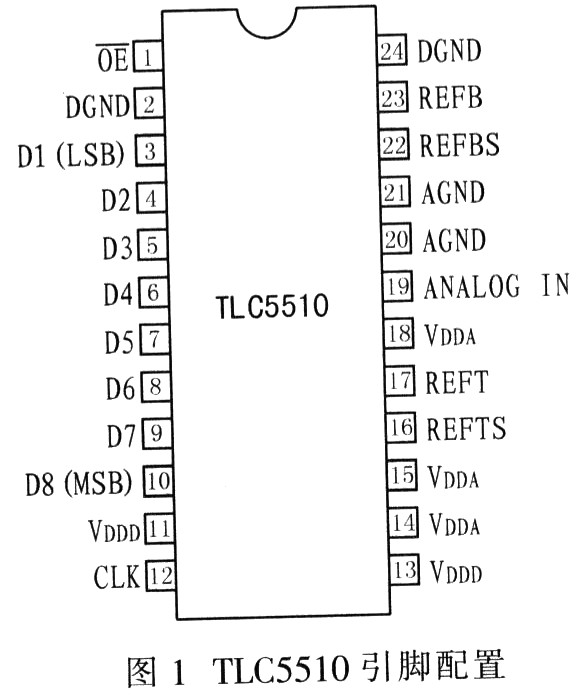

TLC5510是美国TI公司生产CMOS,8位高阻抗并行的模数转换器件(ADC)。它采用+5 V单电源工作,能提供的最大采样率为20 MSPS。TLC-551O的满输入量程是2 V,TLC551OA的满输入量程是4 V。TLC5510采用了半闪速结构及CMOS工艺,所以大大减少了器件中比较器的数量,并在高速转换的同时能够保持较低的功耗。在推荐的工作条件下,TLC5510的功耗仅为130 mW。

TLC5510模数转换器内含时钟发生器、内部基准电压分压器、1套高4位采样比较器、编码器、锁存器、2套低4位采样比较器、编码器和1个低4位锁存器等电路。TLC5510的外部时钟信号CLK通过其内部的时钟发生器可产生3路内部时钟,以驱动3组采样比较器。基准电压分压器则可用来为这3组比较器提供基准电压。输出A/D信号的高4位由高4位编码器直接提供,而低4位的采样数据则由2个低4位的编码器交替提供。 TLC551O的工作时序如图2所示。时钟信号CLK在每一个下降沿采集模拟输入信号。第N次采集的数据经过2.5个时钟周期的延迟后送到内部数据总线上。此时如果输出使能端OE有效,则数据可送至8位数据总线上。本文引用地址://m.amcfsurvey.com/article/195048.htm

TLC5510不仅具有高速的A/D转换功能,还带有内部采样和保持电路,从而大大简化了外围电路的设计。只需要使用内部基准电阻和VDDA构成基准分压器即可实现2V的满量程转换范围。因为正常的复合视频信号最大电压值不超过2V,所以在本系统设计过程中,将TLC5510的REF-BS端短接至REFB端,REFTS端短接至REFT端,从而获得2V基准电压。视屏信号从ANALOGIN引脚输入,同时采用4MHz的有源晶振提供时钟信号。通过计算可知,该芯片在单行视频信号扫描时间内可进行200次的A/D转换,对于简单图像算法而言,横向分辨率已完全能够满足要求。如果提高TLC5510工作时钟频率,可以继续提高横向分辨率。若使TLC5510工作在极限情况下(20 MHz的采样率),横向分辨率可达到约800个点,也就是30万像素以上。上电以后,由于将TLC5510的OE引脚接到GND,芯片始终处于低有效状态,所以A/D转换将持续工作。8位数据输出直接接到下一级FIFO存储器的输入,由处理器决定存储器是否将A/D转换数据写入。

具体的应用电路如图3所示。需要注意的是,因为TLC5510的AGND引脚和DGND引脚在内部没有连接,所以在外部需要连接。建议采用电感或磁珠连接,用以去除模拟地对数字信号的噪声。同时,在VDDA与AGND,VDDD与DGND引脚之间,应分别使用0.1 μF的电容去耦,建议使用陶瓷电容,并配以10 μF以上的钽电容储能。

模拟信号相关文章:什么是模拟信号

晶振相关文章:晶振原理

摄像头相关文章:摄像头原理

评论