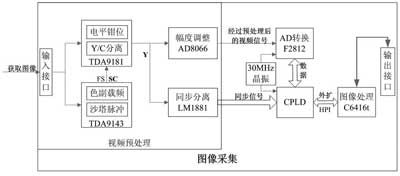

基于高速A/D转换器的视频数据采集系统

2.2 FIFO存储器

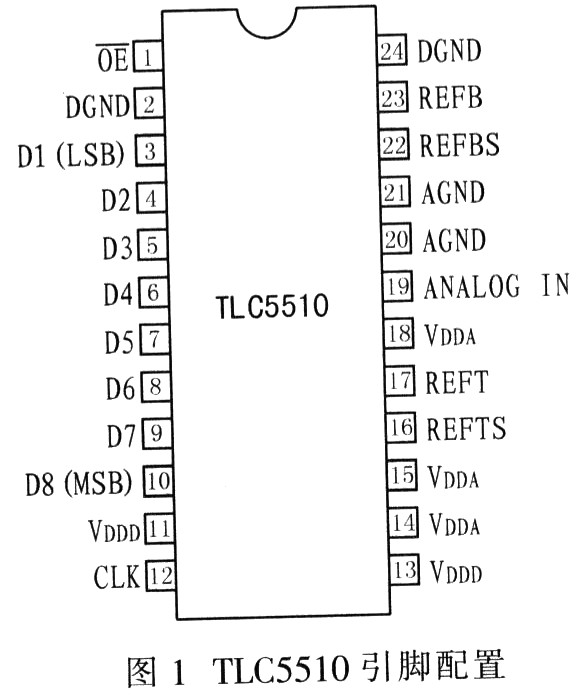

uPD42280是一种2 Mbit的双口FIFO(先入先出)存储器。在本系统中作为A/D转换数据的缓存,容量大且性价比较高,能满足一帧图像数据约25万个像素点存储的要求。A/D转换数据按照一定的时钟节拍顺序写入或读出,它的读写时钟速率最高可达33 MHz。uPD42280本身的数据是8 bit并行输入输出,通过控制它的WE引脚、WRST引脚、RE引脚和RRST引脚的电平高低,实现数据的写入和读取。图4为uPD42280的读、写周期时序。本文引用地址://m.amcfsurvey.com/article/195048.htm

在写控制周期,WE若处于低有效状态(WRST此时为高电平),数据在下一周期上升沿到来前写入存储器地址中;WE若处于高禁能状态。写入暂停,写地址指针保持。在WE处于低有效状态时。若WRST处于低电平,则写地址指针将从当前地址回到地址0,WRST回复高电平后,数据也将从地址0开始写入。在读控制周期,RE若处于低有效状态(RRST此时为高电平),数据在下一周期上升沿到时被读取;RE若处于高禁能状态,读取暂停,读地址指针保持。在RE处于低有效状态时,若RRST处于低电平,则读地址指针将从当前地址回到地址0,RRST回复高电平后,数据也将从地址0开始读取。

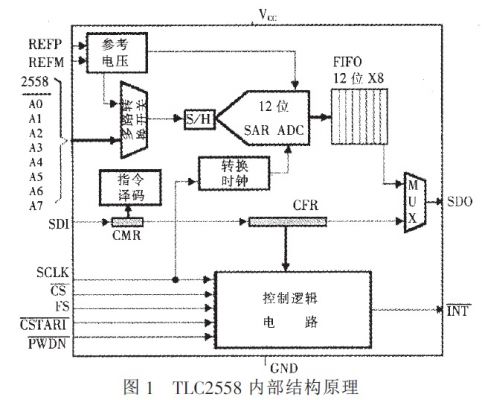

在本系统中,uPD42280的读写时钟与TLC5510的工作时钟使用同一信号源(4 MHz),既保证了FIFO的写操作与A/D转换操作的同步,避免出现数据漏接或混接现象,又可以使数据读取时,读取速率仅由处理器IO口的读取时间决定。通过处理器IO口控制读、写使能信号,读、写地址复位信号,可完成一帧图像数据的读写和更新。在处理器的总线频率为32 MHz时,单行视屏信号扫描时间内(约50 us),IO口最终可读入约190个有效像素的灰度值。去除行消隐区和图像中心对正需要省略的点,本系统每行视频信号可采集到的有效像素点为160个。

需要注意的是,uPD42280本身外围电路很简单,只需要在电源与地之间加1个去耦电容即可。但是由于FIFO存储器有别于RAM,是不能进行内部寻址操作的,只能是简单的地址复位。所以在软件控制时一定要注意逻辑,严格按照读写时序去控制4个引脚,才能保证一场图像的完整写入和读取。

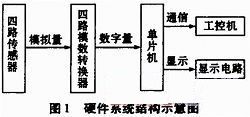

本系统创新之处在于将高速A/D转换器TLC5510与FIFO存储器uPD42280联合使用,实现视频信号的转换和数据存储。这样做使得整个前端的转换和存储完全由几个IO口控制,对单片机本身的性能要求低、资源要求少,仅仅用到了单片机的两路中断和多路普通IO口。这样的设计使得本系统移植性很强,可用于多种单片机或DSP。并且这两款核心器件都是8 bit并行数据输入输出,速度很快,可以实现视频数据的高速传输。

3 软件流程

软件部分主要包括初始化、写操作、读操作和图像处理。首先将处理器的IO口,中断口初始化,PORTB8位作为数据入口,输入使能;PORTK0~PORTK3作为存储器的读写使能和地址控制线,输出使能,PORTJ0、PORTJ1分别响应行、场中断,上升沿触发。

模拟信号相关文章:什么是模拟信号

晶振相关文章:晶振原理

摄像头相关文章:摄像头原理

评论