智原发表PowerSlash(TM)硅智财于联电55奈米超低功耗製程支援物联网应用开发

联华电子今(12日)与ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)共同发表智原科技于联电55奈米超低功耗製程(55ULP)的PowerSlash™基础IP方案。智原PowerSlash™与联电製程技术相互结合设计,为超低功耗的无线应用需求技术进行优化,满足无线物联网产品的电池长期寿命需求。

本文引用地址://m.amcfsurvey.com/article/201610/311235.htm智原科技行销暨投资副总于德旬表示:「物联网应用建构过程中,效能往往受制于低功耗技术。而今透过联电55奈米超低功耗技术以及智原PowerSlash™ IP的加速模式(Turbo Mode)功能,为物联网应用环境带来至关重要的解决方案,除了省电更提供绝佳的效能。再次,联电和智原共同缔造了成功的晶片服务技术。」

智原PowerSlash™ IP包含多重临界电压元件库、记忆体编译器和电源管理元件,能够充分利用联电55ULP的优势在0.81V至1.32V广域电压下运作。此外,新的加速模式功能可以有效调升性能曲线,帮助MCU核心于达到2倍效能,在相同额定时脉下减少约40%的动态功耗。

联电硅智财研发暨设计支援处的莫亚楠资深处长也表示:「物联网晶片设计师对于有效的节能解决方案有高度的需求。联电拥有晶圆代工业界中最健全的物联网专属55奈米技术平台,结合完整的硅智财方案,可以支援物联网产品的不间断低功耗要求。藉由智原在我们的55ULP平台上发表的PowerSlash™ IP,能够让客户使用完善的製程平台,协助提供物联网产品的独特需求。」

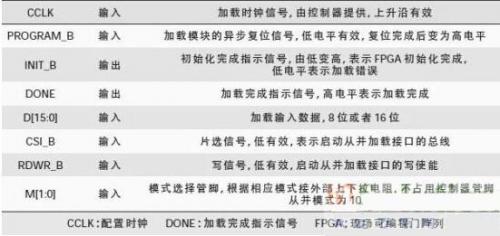

PowerSlash™ IP结合智原的低功耗设计系统、系统单晶片超低功耗控制元件与FIE3200 FPGA平台,可以使用在低功耗积体电路的前端设计或后端开发阶段。联电的55ULP技术能够支援较低的操作电压及sub-pA装置漏电,为含有钮扣电池的产品提供理想的的晶圆製程。智原与联电合力的超低功耗解决方案,为超低功耗积体电路设计平台带来新的基准。

评论