东芝凭借超低功率神经形态处理器推进了深度学习

东芝公司通过开发“时域神经网络1”(TDNN)继续履行其关于促进物联网和大数据分析的承诺,TDNN采用了超低功耗神经形态半导体电路以执行深度学习处理。不同于传统的数字处理器,TDNN包含有大量的采用了东芝原创模拟技术的微小处理单元。我们在11月8日于日本举行的A-SSCC 2016(2016年亚洲固态电路会议)会议上对TDNN作了报告,A-SSCC是由IEEE主办的半导体电路技术国际会议。

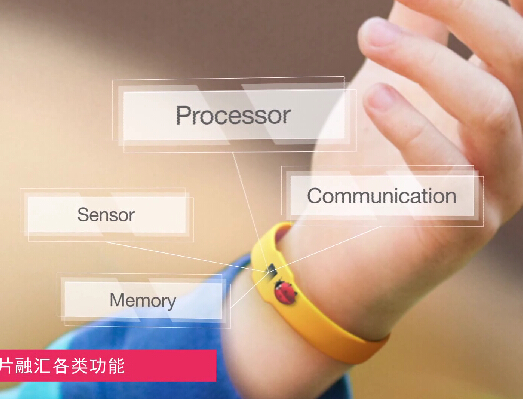

本文引用地址://m.amcfsurvey.com/article/201612/341884.htm深度学习需要大量的计算,特别是在高性能处理器上执行计算,需要消耗大量的电能。但是若要让传感器和智能手机等IoT边缘设备实现深度学习功能,这就需要使用既能执行大量所需操作而又只消耗超低电能的高效节能型IC。

对于冯·诺伊曼式2计算机结构,在从片上或片外存储器装置移动数据到处理单元时将消耗大量电能。减少数据移动的最有效方式是具备大量的处理单元,每个处理单元只专注于处理其附近的一个数据。这些数据点在输入信号(例如:一只猫的图像)转换成输出信号(例如:作为猫的形象的识别)的过程中会给定一个权重。数据点与期望的输出越接近,给定的权重越大。该权重提供了一个自动引导深度学习过程的参数。

大脑具有类似的结构,其中神经元之间的耦合强度(权重数据)被构建于突触(处理单元)中。在这种情况下,突触即是神经元之间的连接,且每个连接具有不同的强度。该强度(权重)决定了通过连接的信号。突触以这种方式执行了一种处理操作。这种结构可以称为完全空间铺展架构,它非常具有吸引力,但也有一个明显的缺点:将其复制到一个芯片上时需要大量的算术运算电路,这将使得电路变得太过庞大。

东芝的TDNN从2013年开始开发,采用了时域模拟和数字混合信号处理(TDAMS3)技术,它可实现处理单元的小型化。在TDAMS中,使用数字信号通过逻辑门的延迟时间作为模拟信号,可有效地执行如加法这样的等算术运算。利用这一技术,深度学习的处理单元可仅由三个逻辑门和一个具有完全空间铺展架构的1位存储器组成。东芝已制造了采用SRAM(静态随机存取存储器)单元作为存储器的概念验证型芯片,并已展示了对于手写数字的识别功能。每次操作的能耗为20.6fJ4,这仅相当于之前一场顶级会议5中所报道能耗的1/6。

东芝计划开发TDNN作为电阻式随机存取存储器(ReRAM)以进一步提高能量和面积效率。其目标是应用于边缘设备并实现高性能深度学习技术的IC。

1. TDNN:使用时域模拟和数字混合信号处理技术的神经网络。

2. 冯·诺伊曼式:标准的、使用最广泛的计算机结构。该结构将数据从存储设备加载到处理单元进行处理。

3. TDAMS:一项模拟信号处理技术,即使用数字信号通过逻辑门的延迟时间作为模拟信号。 由东芝开发。

(参考:http://www.toshiba.co.jp/about/press/2013_02/pr2101.htm)

4. 20.6fJ:相当于1秒内执行48.6万亿次的操作,功耗为1W。

5. ISSCC 2016(国际固态电路会议2016)页号24.2

1. TDNN:使用时域模拟和数字混合信号处理技术的神经网络。

2. 冯·诺伊曼式:标准的、使用最广泛的计算机结构。该结构将数据从存储设备加载到处理单元进行处理。

3. TDAMS:一项模拟信号处理技术,即使用数字信号通过逻辑门的延迟时间作为模拟信号。 由东芝开发。

(参考:http://www.toshiba.co.jp/about/press/2013_02/pr2101.htm)

4. 20.6fJ:相当于1秒内执行48.6万亿次的操作,功耗为1W。

5. ISSCC 2016(国际固态电路会议2016)页号24.2

评论