EUV 的单次曝光与多次曝光的进步

随着半导体器件变得更加复杂,它们的图案化方法也变得更加复杂。每个新节点的极小特征尺寸要求光刻技术不断进步。尽管自行业成立以来基本的光刻过程没有改变——通过光罩将光照射到准备好的硅晶圆上——但该过程中每个部分的技术和方法都发生了巨大变化。随着极紫外(EUV)光刻技术在过去五年从实验室过渡到 7 纳米和 5 纳米的大规模生产,这些进步加速了。现在,随着高数值孔径(high-NA)EUV的即将到来,对于 3 纳米节点及以下的单图案与多图案技术之间的辩论已经加剧。

本文引用地址://m.amcfsurvey.com/article/202407/460611.htmEUV多图案光刻技术的独特之处在于,决定使用单图案还是多图案需要考虑所需的剂量,以使晶圆曝光并仍然可制造。单图案光刻过程可能比双图案过程更昂贵,因为单图案可能需要超过两倍的曝光剂量,并且在非常昂贵的扫描仪上比双图案过程具有更差的吞吐量。

推动单次曝光的极限

单次曝光涉及使用单一曝光步骤在晶圆上创建所需的图案,与多图案方法相比,减少了工艺步骤和相关成本。这项技术因其简单性和成本效益而长期受到半导体制造商的青睐。单次曝光的一些好处包括:

降低缺陷风险:与多图案相比,单次曝光的缺陷风险降低,多图案可能引入对齐问题、叠加误差和其他可能影响产量的缺陷。通过最小化工艺步骤的数量,单次曝光本质上降低了这些风险,从而实现更高的产量和更可靠的制造结果。

提高吞吐量:多图案需要几次光刻和刻蚀周期,每次都会延长整体工艺时间。相比之下,单次曝光简化了制造流程,允许更快地处理晶圆。

降低成本:多图案中每次额外曝光都需要额外的掩模和增加使用先进的光刻工具,从而推高成本。通过减少所需的曝光次数,单次曝光可以大幅节省材料和设备使用。

简化过程控制:在多图案中管理过程参数并确保多次曝光的一致性可能具有挑战性。单次曝光简化了过程控制,使其更容易在制造过程中保持一致性和可重复性。

制造商非常努力地使单次曝光工作,因为没有人想做双次曝光,这太昂贵了。所以在过去五年里确实发生了这种情况。公司尽可能地推动单次曝光技术,推迟了双次曝光的需求,比任何人预期的都要长。

EUV 扫描仪质量的逐步改进在将单次曝光扩展到五年前ASMLNXE:3400C 扫描仪刚刚推出时所不可能的范围内发挥了关键作用。从那时起,功率和扫描仪技术的进一步进步,包括更好的镜头和更复杂的照明器,有助于降低缺陷率和提高产量。这些改进提高了单次曝光的实际分辨率,使其成为更小特征尺寸的更可行选择。

ASML推出了一系列 0.33 NA EUV 光刻设备模型,每次他们这样做,它们的吞吐量就会略有提高,叠加效果更好,镜头也更好。现在他们正在发货 3800,每一款的可靠性都在不断提高。

ASML最新的 EUV 设备的更高源功率使使用更高剂量成为可能,这反过来又提高了分辨率并降低了缺陷的可能性。此外,新光刻胶技术的进步提高了灵敏度和分辨率,允许在更小的间距上进行更精确的图案化。

除了提高 EUV 扫描仪本身的规格外,193 纳米干法和浸没式光刻中使用的一些技巧也已应用于 EUV,以支持更紧密的间距。许多这些是分辨率增强技术(RET)、源和掩模优化(SMO)、更积极的光学接近校正(OPC)甚至是曲线 OPC,加上逆光刻技术(ILT),无论是曼哈顿化还是曲线化,用于热点。

曾经在 32 纳米间距上具有挑战性的事情现在在 30 纳米上变得具有挑战性,而在 30 纳米上具有挑战性的事情现在在 28 纳米上变得可以管理。尽管使用单次曝光实现真正的 28 纳米间距仍然很困难,但 EUV 工具和抗蚀剂能力的改进使我们接近了。

但是,尽管单次曝光很受欢迎,但它也有缺点。在更小的节点上,单次曝光在实现高精度的更细间距方面存在困难。随着特征尺寸的缩小,误差的余地减小,使得保持图案保真度和控制缺陷变得更加困难。在这些尺度上,光子吸收的随机性也可能导致变化,从而产生缺陷,随着关键尺寸的缩小,这些问题变得更加严重。此外,单次曝光在这些更小间距上所需的更高剂量可以显著增加整体工艺成本并降低吞吐量。

制造商希望尽可能低地推动单次曝光,因为它更具成本效益。但这并不总是那么容易,因为要使单次曝光提供良好的产量通常需要更高的成像剂量,而更高的剂量增加了成本。现在你有一个更高成本的单次曝光与一个更高成本的双次曝光相比,了解确切的权衡点可能变得棘手。

多图案化

虽然单次曝光提供了几个优点,但它在更小的节点上也有明显的局限性。随着特征尺寸的不断缩小,行业越来越多地转向多图案化技术,以实现在 3 纳米及以下先进节点上所需的精度和保真度。

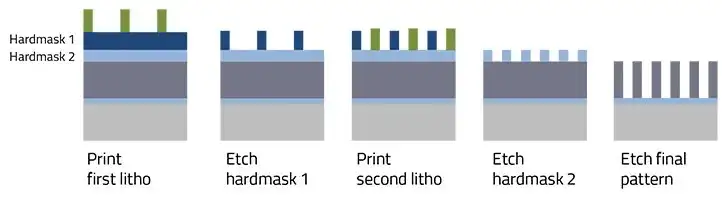

双图案化本质上比单次曝光更复杂和昂贵,但对于在先进节点上实现最小特征至关重要。它需要多个硬掩模和多次曝光,但如果你有一个宽松的间距并且你正在进行双图案化,你可以使用更低的剂量,这意味着每层的吞吐量比单次曝光更高。所以成本上有一点抵消。

图 1:双重图案会增加密度。来源:Lam Research

该行业多年来一直使用浸没光刻进行多图案化,积累了大量关于分解设计布局和自对准工艺的知识。多图案化的原则无论是对于 193 浸没还是 EUV 都是相同的,但要实现在 3 纳米节点及以下实现产量目标所需的过程控制和精度水平需要新策略。

过程控制和 AI

多图案化的一个重大挑战是管理多次曝光,并确保最终图案的整体性能符合所需规格。多次曝光增加了控制困难,使得保持图案保真度和一致性更加困难。此外,使用这些技术与昂贵的 EUV 工具进一步复杂化了成本权衡。

先进的光刻技术有超过 1000 个设备和过程参数需要进行表征和监控,以获得质量结果。这种需求正在加速 EUV 发展周期,为人工智能(AI)系统开发,这些系统能够优化多图案化光刻并改善这些先进节点上的叠加误差等过程问题。

此外,自对准双图案化(SADP)和自对准四图案化(SAQP)等多图案化技术对于在 3 纳米及以下所需的精细特征的生产是必要的。

自对准双图案化(SADP)涉及使用单一光刻曝光,然后进行一系列沉积和刻蚀步骤来创建图案。该过程通常从在预制图案特征的侧面沉积间隔材料开始。然后使用该间隔作为后续刻蚀步骤的掩模,有效地将单次曝光最初图案化的特征数量翻倍。

SADP EUV 过程还可以利用 EUV 的高光刻分辨率创建非常紧密的线端间距和其他设计师所需的节省面积的功能。然而,需要先进的制造工具,如逆光刻技术(ILT),以高度优化掩模图案,减少晶圆上电路特征的最小尺寸和间距。

自对准四图案化(SAQP)扩展了 SADP 的原则,以实现更小的特征尺寸。SAQP 涉及额外的间隔沉积和刻蚀周期,有效地将原始光刻曝光的图案密度增加四倍。这种方法特别适用于创建 3 纳米及以下所需的极细间距。

该行业多年来一直使用浸没光刻进行多图案化,积累了大量关于分解设计布局和自对准工艺的知识。这些技术和经验教训可以与 EUV 光刻一起重新使用。并不是说 EUV 有任何新技巧。相反,随着我们向更小尺寸的移动,对更高水平的过程控制和精度的需求变得更加关键。

EUV 掩模创新

在过去五年中,EUV 掩模制造的基础设施和技术有了显著改进,以满足 7 纳米和 5 纳米节点的严格要求。EUV 光刻技术的采用推动了光学接近校正(OPC)和 ILT 的发展,这对于管理数据量和确保精确检查 EUV 掩模特征至关重要。

ASML 在提高 EUV 膜片的性能方面也取得了显著进展,实现了 83% 至 84% 的传输率,显著提高了整体缺陷性和传输精度。EUV 掩模的整体质量也有所提高,使 EUV 光刻更适合大规模生产。

看来 Hoya 和 Asahi Glass 现在正在制造足够多的无缺陷掩模空白,人们实际上可以考虑用某些类型的掩模进行曝光。这在几年前是不可想象的。考虑到五年前生产一个没有缺陷的 EUV 掩模空白是一个重要的里程碑,无缺陷掩模空白的改进是显著的。

曲线掩模和多图案化

曲线掩模因其潜在的提高设备性能和降低功耗而受到广泛关注。曲线特征允许更有效的设计,从而在最终设备中实现更高的性能和更低的功耗。然而,将曲线特征整合到多图案化过程中还有很长的路要走。设计曲线掩模的计算复杂性已经需要 GPU 加速和 AI 支持,并且随着多图案化的增加,这种复杂性呈指数级增长。

曲线掩模图案最初是由曲线 ILT 驱动的,以获得最佳分辨率和工艺窗口,并由多束掩模写入器实现。由于所有 EUV 掩模都是由多束掩模写入器编写的,它们也可以是曲线的。特别是 OPC 很容易从基于段的曼哈顿 OPC 扩展到基于控制点的曲线 OPC,公司正忙于将曲线掩模应用于 EUV 和 DUV 层,以缩小节点并提高产量。行业面临的下一个要求是需要将 ILT 扩展到 EUV 的全芯片或全缝曲线 ILT。一旦有 ILT 产品能够做到 EUV 的全缝曲线 ILT,它将被行业采用。

管理这些复杂性的一种方法可能是尽可能简单地保持拼接边界,边界本身具有最小复杂特征,并且更复杂的曲线特征在半尺寸光罩中,类似于在多芯片模块中采取的方法。这种方法有助于保持对齐和叠加精度,这对于在先进节点上多图案化的成功至关重要。它确保了关键特征在拼接过程中不会受到影响,保持了最终设备的完整性和性能。

即使这是可能的,也需要一段时间来解决具有曲线特征的多图案化的解决方案。在这些尺度上的光刻物理,包括管理 3D 效果和非单色光源,为过程增加了巨大的复杂性。

High NA EUV

未来几年内引入的 High NA EUV 光刻将通过提供更高的分辨率和改进的图案保真度,显著影响图案化领域。High NA EUV 技术旨在减少对多图案化的需求,将单次曝光扩展到 3 纳米及更远。然而,过渡到 High NA EUV 带来了自己的一套挑战,需要大量的技术和财务投资。

High NA EUV 的主要优点是其能够实现更细的分辨率,将半导体制造的边界推向了埃拉。然而,这种增加的分辨率带来了新的挑战,特别是在管理随机效应和发展新的抗蚀剂材料方面,这些材料能够在图案化更薄层时承受更高的剂量。

对于 14 埃和 10 埃节点,行业将使用 High NA EUV,这需要双曝光拼接来制造大尺寸芯片。High NA EUV 将需要创新的拼接和叠加控制解决方案,以及先进的抗蚀剂材料来应对更紧密的过程窗口。

High NA EUV 面临的一个主要挑战是开发合适的抗蚀剂材料,主要是金属氧化物。这种从传统的化学放大抗蚀剂到金属氧化物抗蚀剂的转变对行业来说是一个重大变化。虽然金属氧化物抗蚀剂由于其在更小节点上的更高分辨率和灵敏度而提供改进的性能,但它们尚未准备好进行大规模生产。

尽管如此,High NA EUV 技术的发展速度比预期的要快。他们今年夏天就用这些工具成像,这真是相当了不起。但是 High NA EUV 基础设施的高初始投资是一个重大障碍,更不用说运营的持续成本了。公司将不得不权衡这些成本与潜在的好处。

结论

在过去五年中,EUV 光刻取得了显著进展,特别是在单次和双次图案化领域。这些进步对于实现更小节点的先进半导体器件的生产至关重要。随着行业向采用 High NA EUV 工具的方向发展,持续的创新和合作将是克服新挑战并实现这些尖端技术的全部潜力所必需的。

EUV 光刻中单次和多图案化之间的持续辩论突显了半导体制造的动态性质。在 3 纳米节点及以后,两种方法都将发挥关键作用,由技术进步和经济考虑塑造。

评论