嵌入式系统数字图像采集接口电路设计

四、内存直接写入接口设计

在处理器速度较慢且图像数据输出的频率不能降低的情况下,采用上述I/O接口方法不能得到完整的图像。另外,有些应用中要求能够实时采集图像。为此,我们设计了高速数据图像采集方法?内存直接写入法。由于SRAM访问控制简单,电路设计方便,被大量嵌入式系统采用,本文以SRAM作为存储器。

1、电路原理和结构

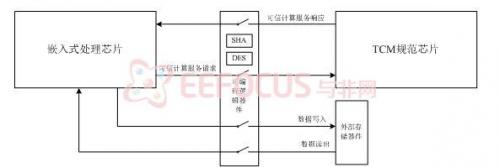

内存直接写入方法通过设计的图像采集控制器(以下简称控制器)不需处理器参与,直接将图像数据写入系统中的内存中,实现高速图像采集。

图5是接口结构图,当需要采集图像时,处理器向控制器发出采集请求,请求信号capture_r从高到低。控制器接到请求脉冲后,发出处理器挂起请求信号HOLD,使处理器的外总线处于高阻状态,释放出总线。控制器收到处理器应答HOLDA后管理总线,同时检测图像同步信号。当检测到图像开始位置时,控制器自动产生地址和读写控制信号将图像数据直接写入内存中。图像采集完成后,控制器自动将总线控制权交还处理器,处理器继续运行,控制器中与采集相关的状态复位。控制器可以根据同步信号或设定的采集图像大小确定采集是否完成。![]()

在图5中,控制器包括同步信号检测、地址发生器、SRAM写控制器、总线控制器和处理器握手电路等主要部分。同步信号检测确定每一场(帧)和每一行的起始位置;地址发生器产生写SRAM所需的地址;SRAM写控制器产生写入时序;总线控制器在采集图像时管理总线,采集完成后自动释放;处理器握手电路接受处理器命令、发总线管理请求和应答处理器。

2、SRAM写控制时序

采集图像过程中,控制器自动将数据写入到硬件设定的内存中。写内存时,控制器产生RAM地址(A)、片选信号(/CS)、读信号(/RD)和写信号(/WD),同时锁存传感器输出的数据并送到数据总线(D)上。每写入一个数据后,地址(A)自动增1。采集时/CS保持有效(‘0’)状态而/RD处于无效状态(‘1’)。地址A的变化必须与/WD和数据锁存器协调好才能保证图像数据的有效性。

图6是控制器产生的SRAM信号时序图。用PCLK作为地址发生器的输入时钟,且在其上升沿更新地址值。同样,在PCLK的上沿锁存数据并输出到总线上。将PCLK反相,作为/WD信号,使得在/WD的上升沿地址和数据稳定,确保写入数据的有效性。

3、控制器主要功能的VHDL描述

描述控制器中全部功能的VHDL代码较长,而且有些部分是常用的(如计数器等)。图像采集状态产生和同步信号的检测是其中重要的部分。下面介绍这两部分的VHDL描述。

图像采集状态 capture_s:

处理器的采集请求信号capture_r使capture_s从‘0’到‘1’,场地址发生器(计数器)的溢出位vcount_o,清除capture_s。

process (capture_r, reset, vcount_o)

begin

if reset='0' or vcount_o='1' then

capture_s='0'; -- 清除

else if capture_r'event and capture_r='0' then

capture_s='1'; -- 置状态位

end if;

end process;

同步信号检测:

评论