SHARC并行系统软件设计方法

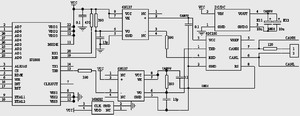

ADSP2116X提供了独立的6个链路口,每个链路口可以实现与其他ADSP2116X或者外围设备点对点的通信。每个链路口包括8位双向数据线(LxDAT7~0),1个双向时钟信号(LxCLK),1个双向确认信号(LxACK)。但是,链路口没有为发送和接收提供2套管脚,所以在任何时刻链路口只能工作在单工状态。依靠链路口进行双DSP间的数据传递时,只需要把2个DSP的10个管脚对应连接即可,不需要任何外部附加逻辑。

在ADSP2116X内部有6个链路缓冲器。用户通过定义LAR寄存器,可以为每个链路口选择一个或几个缓存器。链路缓冲器一端与内部总线相连,另一端通过LAR寄存器与不同的链路口相连。需要注意的是,链路口与链路缓存器是完全不同的概念。链路缓冲器可以理解为一个双向的FIFO,而链路口仅仅代表其对外的10个管脚。链路口的特性很大程度上是由其正在使用的缓冲器的特性决定的。

ADSP2116X的链路口发送时钟频率可以通过LCTLx寄存器的LxCLKD位设置(1,1/2,1/3,1/4核时钟频率),链路口数据线根据需要可以选择为8位或4位。发送方在时钟LxCLK的上升沿送出8/4位码,接收方利用时钟下降沿锁存8/4位码,并且接收方使LxACK有效,表示已准备好接收下一个字。在每个字开始发送时,发送方如果看到LxACK无效,则将LxCLK保持为高,并等待LxACK有效后才开始发送新字。当发送缓冲为空时,LxCLK将保持为低电平。

链路口数据传输可以通过DMA方式和内核直接访问二种方式。DMA方式传输时不需要内核干预,在传输数据量比较大时效率很高,但是需要首先进行DMA参数设置。当仅有个别数据需要通过链路口传递的情况下,往往不使用DMA方式,而是通过ADSP2116X的内核直接访问。用户可以通过LCOM寄存器中缓冲器的状态来控制内核对链路口缓冲进行读写操作,也可以通过相应的中断从链路口缓冲器中读写数据,如“DM(LBUF0)=R0;”或者“R0=DM(LBUF0);”等。值得注意的是,无论是试图从一个空的链路缓冲中读,还是试图向满的缓冲中写,内核的指令都会挂起,直到操作成功为止。因此,内核指令直接读写链路缓存时,需要首先判断链路缓冲状态。

ADSP2116X为每个链路口提供了一个专用的DMA通道,它们分别占用DMA中的4~9通道。链路口的DMA使用非常方便,只需将对应的DMA参数寄存器(IIx,IMx,Cx)设置完毕,使能LCTLx中对应通道的LxDEN即可。在当前DMA结束(或者链式DMA全部结束)后,会触发一个可屏蔽中断通知用户。启动链路口DMA的顺序如下:

(1)由LAR寄存器的AxLB为链路口分配一个LBUFx;

(2)由LCTL寄存器的LxEN使能这个LBUFx,并设置好LCTL控制寄存器;

(3)设置DMA参数(IIy,IMy,Cy);

(4)置位LCTL寄存器的LxDEN,就启动了DMA。

其中:x=0~5,y=4~9。

下面给出一个利用链路口DMA发送数据的示例。

例2:利用链路口0进行数据发送。

.SECTION/dm dm_data;

.VAR trans_data[size];

.SECTION/pm pm_code:

……

r0=0x0002c688;

dm(LAR)=r0;

r9=0x00000229; /*LBUF0使能、发送、8位字宽、核时钟速率*/

dm(LCTL0)=r9;

r0=trans_data;

dm(II4)=r0; /*需要发送数据的起始地址*/

r0=1;

dm(IM4)=r0;

r0=size;

dm(C4)=r0;

ustat1=dm(LCTL0);

bit set ustat1 L0DEN; /*启动发送DMA*/

dm(LCTL0)=ustat1;

如果传输的数据不在一段连续的内存区,而是在多段数据块中,可以利用链式DMA。链式DMA可以在当前DMA操作结束后自动重新配置当前通道并开始新的DMA,所有这些操作都不需要内核的干预。在链式DMA过程中,用户只要对DMA参数配置一次,就可以方便地完成多块数据的DMA传输。

链式DMA是通过CPx寄存器实现的。对于ADSP2116X来说,CPx是一个19位的寄存器。寄存器中低18位表示相对于基地址0x40000的偏移量,用户在这个地址的内部存储器中存放下一次DMA的参数,这些参数叫做TCB(Transfer Control Blocks)。CPx中的第19位是控制当前链式DMA完成后是否产生中断的PCI位。如果把全局地址赋给CPx,则PCI位一定为1,表明一定会产生中断。

评论