NAND闪存的下一个热点:性能

利用50-40nm的工艺制程节点,NAND闪存密度已达到16 GB/D及超过2B/C多级单元(MLC)技术。尽管位元密度强劲增长,但是NAND闪存的编译能力一直停留在10MB/S范围内。由于数字内容需要的增长,公司更加重视改进NAND闪存装置的编译和读取性能,使其比特更高和性能更快,以满足消费者的需要。再加上存储产品价格急剧下降,高比特高性能已成为各个公司努力追求的方向。

本文引用地址://m.amcfsurvey.com/article/87240.htm2008年国际固态电路会议的论文和2007年半导体观察(SI)基于16GB的NAND闪存固态电路分析,都暗示了NAND在结构、性能、设计(挑战3B/C的NAND发展)和工艺技术要求等领域的新发展趋势。

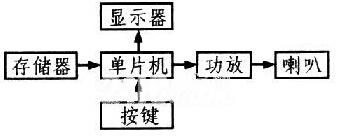

新的体系结构

2007至2008年间,NAND闪存设备和设计体系结构的变化是显而易见的。2008年推出的三种设计都采用了所谓的全位线结构(ABL)。ABL通过将所有位线同时连接到页面缓冲器来提高NAND闪存阵列性能。其性能是传统体系结构计算吞吐量的3.4倍。这是一个大改善,由于新装置的体系结构类似, 56nm工艺制造技术可用于常规设备。在SLC模式,ABL结构可以进一步增加编译的吞吐量,达到60 MB/S。

通过今年发布的3B/C设计显示:一些挑战必须通过增加每单元位数目实现。旋转阵列结构(RAA)是用来压制噪音阵列及改进存储器阵列配电。这是至关重要的3B/C设计,因为容纳8个不同的区域于(如4反向2-bit/cell设计)一个闪存单元需要非常紧密的单元阈值电压分布及精密传感单元数据。

56nmMLC,16千兆位NAND闪存与传统结构。

资料来源:半导体观察

把字线和位线控制信号靠近阵列和传感闪存单元格数据,将字线电压作为接地电压。 3位设计采用了位线和字线电压偏置跟踪,从而提高传感的准确性并且减少传感时间,性能提高了20 % 。编译速度达到8 MB /S,是MLC的80%,给设计带来更多挑战。这种设计创新为56nm16GB的NAND器件( 142平方毫米)提供最小的芯片尺寸。

基于3-bit/cell设计的NAND闪存器件,估计到2009年能占SanDisk/Toshiba产品线的一半。不过43 nm的MLC( 2-bit/cell )技术成本仍然低于56 nm的3-bit/cell技术。43纳米MLC技术是每平方毫米数兆比特,效率高出18 %。

40nm工艺制程的挑战

栅极感应漏极漏电(GIDL)成为使用40nm制造节点的一个重要问题。应尽量减少GIDL对程序所造成的干扰。要做到这一点,可以引入两个虚拟字线加到NAND结尾。为了弥补额外字线增加对芯片尺寸的要求,用较长的NAND串( 64 VS. 32 )来改进面积效率。较长的NAND串也增加串电阻,这就要求在读和编译时进行字线调制。这样可以确保应用适当的字线电压,取决于字线在NAND串中的位置:用较高的字线电压水平作为存取单元放在串(位线)上方附近的 ,以补偿串电阻。

电压缩放

在一个系统中,较低的Vcc对于小几何结构、与其他器件的互操作性是比较理想的。不过,较低的操作电压使得设计电荷泵变得很难,这是NAND闪存装置至关重要的电路模块。目前设计的43nm器件使用两个不同的电压:一个作为内部的运作,另一个为I/O运作。 43nm的设计采用了vcc为3.3伏和vccq为1.8伏。

同步DDR接口

NAND型闪存已经实现异步接口,而接口问题被认为是NAND高性能应用的一个关键瓶颈。英特尔与美光公布了一款NAND闪存接口设计,它具有200 MB/S能力的DDRI/O接口。它基于开放的NAND型闪存接口规格说明(ONFI )。

使用四芯线组平面(或库)架构和4n预取数据路径这两个DDR2 SDRAM的基本技术,该装置可以支持异步接口和DDR2的同步接口。并用SLC技术来提高其编译和读取性能。证实了这一点字线的水平引用的一份文件,该装置的设计。为达到我们的目的,用东芝的56纳米16千兆位MLC器件(即相等于1 8千兆位弹针装置)的共同点作为比较比较。

东芝公司的16千兆位MLC器件比英特尔/美光的8千兆位SLC器件大7 %。鉴于最小特征尺寸之间的工艺差( 56-50 nm的) ,该四芯线组平面架构和DDR2预取数据路径可以忽略不计。以及使用64-cell的NAND串来减小裸片整体面积和DDR2接口架空。在东芝的43纳米设计中也使用两个电源电压:一个作为内部的运作,另一个作为I/O运作( vcc = 3.3伏, vccq = 1.8伏或3.3 V ) 。

而100MB/S的编译速度是一个很高的性能水平,传统的异步接口使用ABL架构(只有SLC模式)可达到60个MB/S。

SLC的性质决定了英特尔/美光的器件非常昂贵,尤其是在消费性应用。截至2008年5月, 8千兆位的SLC NAND型器件几乎比16千兆位的MLC NAND型器件贵了50 %。如固态驱动器、游戏控制台和服务器等高高端应用,或许会成为该新器件的初步目标。

也许,基于MLC的支持,一个基于高预取的更细分的银行体系结构将在NAND闪存器件与DDR接口的价格和性能取一个最佳点。

ABL架构、基于DDR接口的quad-bank结构, 64-cell的NAND串,采用虚拟字线的NAND串,电路设计的创新,周密布局的主电路模块和良好的电压分配将会是在2008年年初宣布一些NAND闪存的创新设计,。

基于DDR2接口的NAND闪存器件(ONFI)似乎提供更高的性能,但将需要更多的架构和电路改进,包括架构的进一步细分(更多库或平面) ,以支持更符合成本效益的MLC NAND技术。

评论