问题现象:

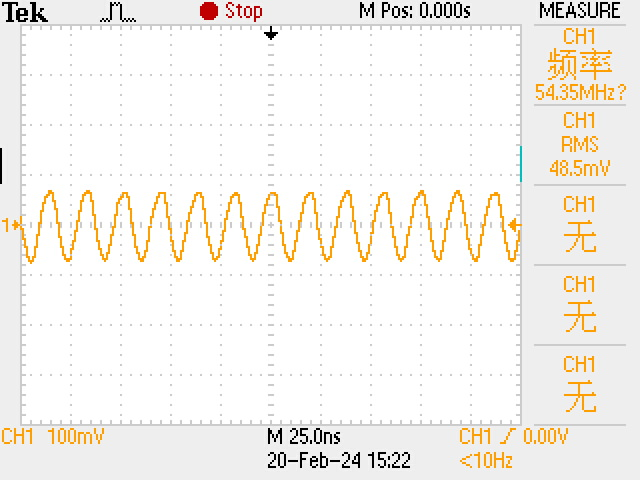

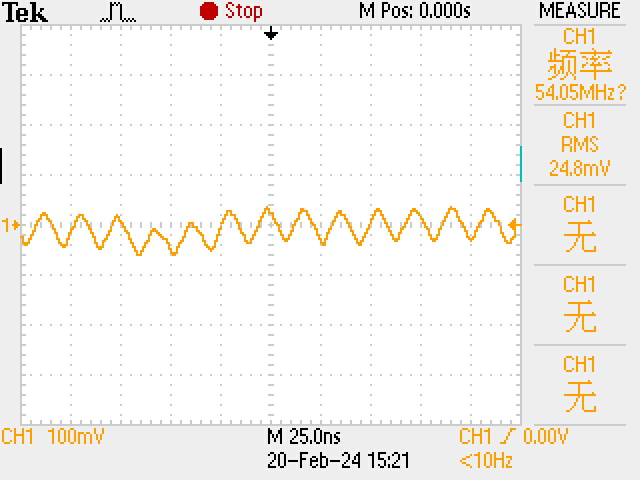

当SOC(927 LVDS输入端)设置为54Mhz时,CLK幅度为48mV左右,但是928 LVDS输出端 CLK幅度出现衰减24mV左右,与927输入信号不一致,

当我们把CLK频率降低为20Mhz时,927输入端与928输出端并不会出现衰减现象。

需求:

LVDS CLK信号传输一致,不出现衰减。

927 LVDS输入端附图:

928 LVDS输出端附图:

| 有奖活动 | |

|---|---|

| 奖!发布技术笔记,技术评测贴换取您心仪的礼品 | |

| 【有奖活动】震撼来袭!这场直播将直击工程师的心灵! | |

| “我想要一部加热台”活动,不花钱赢取开发好工具!活动开始了哦 | |

| 【有奖活动】伙伴们:您的“需求”解决了吗? | |

| 抽奖了,抽奖了,金升阳医疗电源 | |

| 打赏帖 | |

|---|---|

| 放大↔震荡被打赏50分 | |

| 【分享评测,赢取加热台】+Telink-泰凌微电子B91点灯篇被打赏20分 | |

| 【换取手持数字示波器】+DFR0216全彩灯带WS2812示例分享被打赏50分 | |

| 【换取手持数字示波器】安装雅特力国产IDE-AT32IDE被打赏30分 | |

| 【换取手持数字示波器】+DFR0654板卡驱动数码管和串口功能分享被打赏50分 | |

| 【换取手持数字示波器】+DFPlayerMini模块推喇叭示例分享被打赏50分 | |

| 【换取手持数字示波器】+DFR0868模块开发准备工作分享被打赏30分 | |

| 【换取手持数字示波器】HMI开发板首秀RTduino被打赏30分 | |

| 电解电容引发的问题被打赏50分 | |

| 【换取手持数字示波器】+AT-START-F405之串口通讯被打赏40分 | |