- 【摘 要】 介绍一种由单片机控制的采用MAX038芯片构成的高频函数发生器,它的特点是输出精度高,频率范围宽,失真小。

关键词:函数发生器,频率,占空比

1 引 言

在自动控制系统设计及调试过程中,不

- 关键字:设计发生器函数单片机基于

- 1 引言 作为数字通信网的基础支撑技术,时钟同步技术的发展演进始终受到通信网技术发展的驱动。在网络方面,通信网从模拟发展到数字,从TDM网络为主发展到以分组网络为主;在业务方面,从以TDM话音业务为主发展到以

- 关键字:概述技术同步时钟

- #includereg52.h>#define uint unsigned int#define uchar unsigned charsbit key0 = P3^0;//时间调节 ...

- 关键字:1602时钟可调节显示

- 此时间程序没有用到ds1302等芯片,而是用单片机自带的定时器制作的,并且可调整时间。请大家多多指教

#includereg52.h

#include intrins.h

#define uchar unsigned char

#define uint unsigned int

ui

- 关键字:时钟程序可调定时器单片机基于

- 时钟-闹钟-时间控制器 调节方法一、功能: 时钟显示小时、分钟;可调时钟控制输出;三次可调闹铃。二、调节方法:各种参数调节设定方法:第一步:按“功能”键,选择功能1,进入调节状态;第二步:重复按ldq

- 关键字:时钟闹钟调节方法

- 时钟闹铃控制电路说明:1、共阳极四位一体12引脚数码管引脚号是:将数码管的数字面朝向观察者,左下角是第1脚,逆时针方向依次是2、3、4、5、6、7、8、9、10、11、12 脚。 2、如果是单个的数码管或两位一体的数码管

- 关键字:时钟控制电路

- 花了几个小时,完成“时钟温度计” 的程序,在此感谢“康哥”的支持!功能:时钟显示,温度显示,可调时间,按键发 ...

- 关键字:时钟温度计数码管显示

- C8051F320包含一个内部振荡器,也可以采用其他方式提供振荡。手头没有任何元器件,所以只考虑使用内部振荡器。 ...

- 关键字:C8051F320时钟八段管

- 电源、时钟和复位电路图(Altera FPGA开发板)如图所示:

图 电源、时钟和复位电路图(Altera FPGA开发板)

图 时钟电路图(Altera FPGA开发板)

图 复位电路图(Altera FPGA开发板)

- 关键字:FPGA开发Altera电路图时钟复位电源

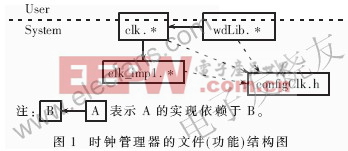

- 嵌入式时钟管理器的设计方案介绍, 目前,在嵌入式产品的研发中,低档微处理器软件多采用裸机开发模式实现。在这种开发模式中,常有如下需求: (1) 在经历特定的时间段后,执行特定操作; (2) 根据给定周期执行特定操作。 传统的作法是利用前

- 关键字:方案介绍设计管理时钟嵌入式

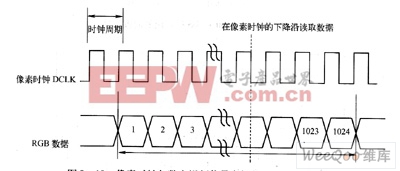

- 只要是数字信号处理电路,就必须有时钟信号。在液晶面板中,像素时钟是一个非常重要的时钟信号。像素时钟信号的频率与液晶面板的工作模式有关,液晶面板分辨率越高,像素时钟信号的频率也越高。在一行内,像素时钟的

- 关键字:DCLK信号时钟像素液晶显示

- 时钟系统是微控制器(MCU)的一个重要部分,它产生的时钟信号要贯穿整个芯片。时钟系统设计得好坏关系到芯片能否正常工作。在工作频率较低的情况下,时钟系统可以通过综合产生,即用Verilog/VHDL语言描述电路,并用EDA

- 关键字:MCU时钟系统

- CPLD中可编程时钟电路,为慢速仪器产生快速仪器等占空比的同步脉冲。同步两个仪器信号时,保证接收器锁存发送器的同步信号是重要的。例如,产生主脉冲信号时,脉冲发生器产生同步脉冲。Avtek的AV-1015B带TTL的50Ome

- 关键字:CPLD发生器仪器

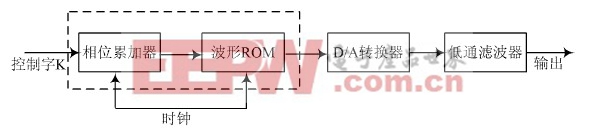

- 标签:FPGA DDS任意波形发生器( Arbit rary Waveform Generato r,AWG) 是一种多波型的信号发生器, 它不仅能产生正弦波、指数波等常规波形, 也可以表现出载波调制的多样化, 如: 产生调频、调幅、调相和脉冲调制

- 关键字:设计研究发生器波形FPGA任意基于

- 电力系统是时间相关系统,无论电压、电流、相角、功角变化,都是基于时间轴的波形。近年来,超临界、超超临界机组相继并网运行,大区域电网互联,特高压输电技术得到发展。电网安全稳定运行对电力自动化设备提出了新的要求

- 关键字:分析电力系统时钟同步技术

时钟(clk)发生器介绍

您好,目前还没有人创建词条时钟(clk)发生器!

欢迎您创建该词条,阐述对时钟(clk)发生器的理解,并与今后在此搜索时钟(clk)发生器的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473