- 西门子数字化工业软件近日推出 Tessent™ RTL Pro 创新软件解决方案,旨在帮助集成电路 (IC) 设计团队简化和加速下一代设计的关键可测试性设计 (DFT) 任务。随着 IC 设计规模不断增大、复杂性持续增长,工程师需要在设计早期阶段发现并解决可测试性问题,西门子的 Tessent 软件可以在设计流程早期阶段分析和插入大多数 DFT 逻辑,执行快速综合,运行 ATPG(自动测试向量生成),以发现和解决异常模块并采取适当的措施,满足客户不断增长的需求。Tessent RTL Pro 进一步扩展了

- 关键字:西门子Tessent RTL Pro可测试性设计

- 西门子数字化工业软件近日推出Tessent Multi-die软件解决方案,旨在帮助客户加快和简化基于2.5D和3D架构的新一代集成电路(IC)关键可测试性设计(DFT)。随着市场对于更小巧、更节能和更高效能的IC需求日益提升,IC设计界也面临着严苛挑战。下一代组件正倾向于采用复杂的2.5D和3D架构,以垂直(3D IC)或并排(2.5D)方式连接多个晶粒,使其能够作为单一组件运作。但是,这种做法为芯片测试带来巨大的挑战,因为大部分传统的测试方法都是基于常规的2D流程。为了解决这些挑战,西门子推出Tess

- 关键字:西门子2.5D3D可测试性设计

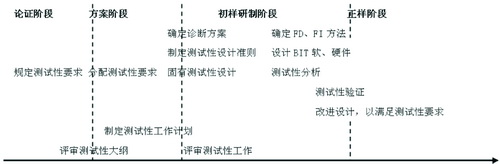

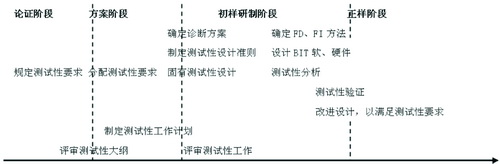

- 从系统测试性设计的角度,分析了国内外测试性设计技术的发展状况、存在的问题;讨论了开展系统测试性设计并制定测试性工作规范在飞行器设计中的必要性;总结了系统测试性设计的一般工作流程;并根据航天产品特点,对测试性设计方法进行探索研究。

- 关键字:系统测试系统级可测试性设计飞行器200806

- 摘 要: 本文论述了边界扫描技术的基本原理和边界扫描在电路板测试及在FPGA、DSP器件中的应用。介绍了为提高电路板的可测试性而采用边界扫描技术进行设计时应注意的一些基本要点。关键词: 边界扫描测试;JTAG;电路板测试;可测试性设计引言电子器件的生产商和电子产品的制造商都在倾向于采用最新的器件技术,如BGA、CSP(芯片规模封装)、TCP(倒装芯片封装)和其它更小的封装,以提供更强的功能、更小的体积,并节省成本。电路板越来越密、器件越来越复杂、电路性能要求越来越苛刻,越来越难的接入问题导致了工业标准

- 关键字:JTAG边界扫描测试电路板测试可测试性设计PCB电路板

可测试性设计介绍

您好,目前还没有人创建词条可测试性设计!

欢迎您创建该词条,阐述对可测试性设计的理解,并与今后在此搜索可测试性设计的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473