在每个指令周期内文章进入在每个指令周期内技术社区

TMS320C31和80C196双CPU构成的高速实时控制

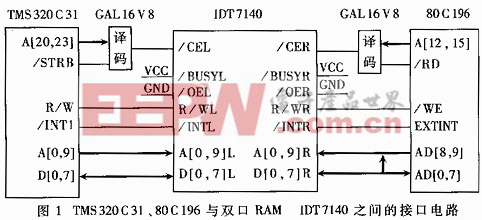

- TMS320C31和80C196双CPU构成的高速实时控制,介绍了采用TMS320C31和80C196双CPU构成的高速实时控制系统的基本构成,给出了TMS320C31、80C196与双口RAM IDT7140之间的接口电路,IDT公司双口RAM系列的中断逻辑设计以及DPS与80C196之间采用双口RAM进行高速数据通信的

- 关键字:DSP 双口RAM 高速实时 中断

DSP也称数字信号处理器。TMS320C31是TI公司的第三DSP芯片它的基本结构包括:(1)程序文凭间与数据空间分开的总线结构可以对程序存储器和数据存储器这两个独立的存储器进行独立编址、独立访问(2)流水线结构以三级流水线操作为例在每个指令周期内三条不同的指令都处于激活状态但处于不同的阶段分别为取指、译码和执行(3)专用的硬件乘法器使乘法可以在单周期内完成(4)特殊的DSP指令(5)快速的指令周期可以达到33.3ns即每秒能执行

| 共1条 1/11 |