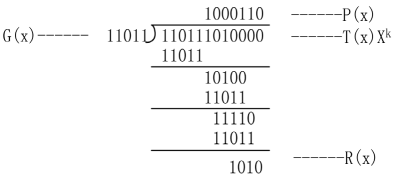

- 在现代数字通信中,要求信息在传输过程中造成的数字差错必须足够低。但由于通信信道存在噪声和传输特性不 理想等原因造成了信号的码间串扰,导致信息在传输过程产 生差错。为了最大限度地保证通信过程中信息的完整性,需 要采用信道编码技术对可能发生的差错进行有效地控制,而 循环冗余校验码就是其中一个最有效的编码技术。1 循环冗余校验码基本思想循环冗余校验码是一种校错能力很强且使用非常广泛 的差错检验方法。循环冗余校验码采用在发送的有用码后面 加入校验码来实现数字通信

- 关键字:FPGA校验码

校验码介绍

您好,目前还没有人创建词条校验码!

欢迎您创建该词条,阐述对校验码的理解,并与今后在此搜索校验码的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473