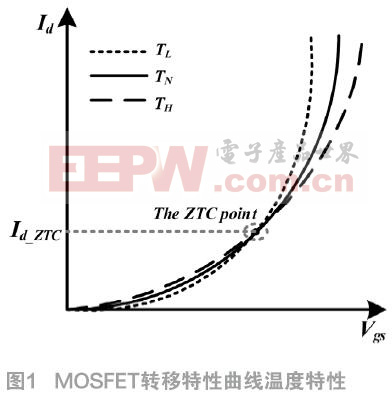

- 基于TSMC40LP工艺设计了一种新颖的温度补偿、高电源抑制比的带隙基准源。本设计采用全MOSFET设计,工作于1.1 V电源电压,通过将MOSFET偏置在零温度系数工作点,并结合温度补偿技术和有源衰减电路,实现在-40 ℃~125 ℃内温度变化系数为6.6 ppm/℃,低频下电源抑制比为93 dB,高频下电源抑制比为56 dB,与此同时,利用阻抗调试对环路稳定性进行了补偿。

- 关键字:带隙基准全CMOS低电源电压曲率补偿高电源抑制比零温系数点201804

高电源抑制比介绍

您好,目前还没有人创建词条高电源抑制比!

欢迎您创建该词条,阐述对高电源抑制比的理解,并与今后在此搜索高电源抑制比的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473