共模扼流圈:从工作原理到重要性能参数

了解这些简单的滤波器如何帮助您在所需信号衰减最小的情况下对抗共模噪声。

本文引用地址://m.amcfsurvey.com/article/202405/458517.htm根据噪声的传导方式,噪声可分为共模或差模。如果我们不能正确识别噪声模式,我们可能会在电路中添加不适当的噪声抑制组件,从而使噪声情况变得更糟。在本文中,我们将讨论共模噪声的解决方案:共模扼流器(CMC),它衰减共模信号,同时允许差分信号在理想情况下不衰减。

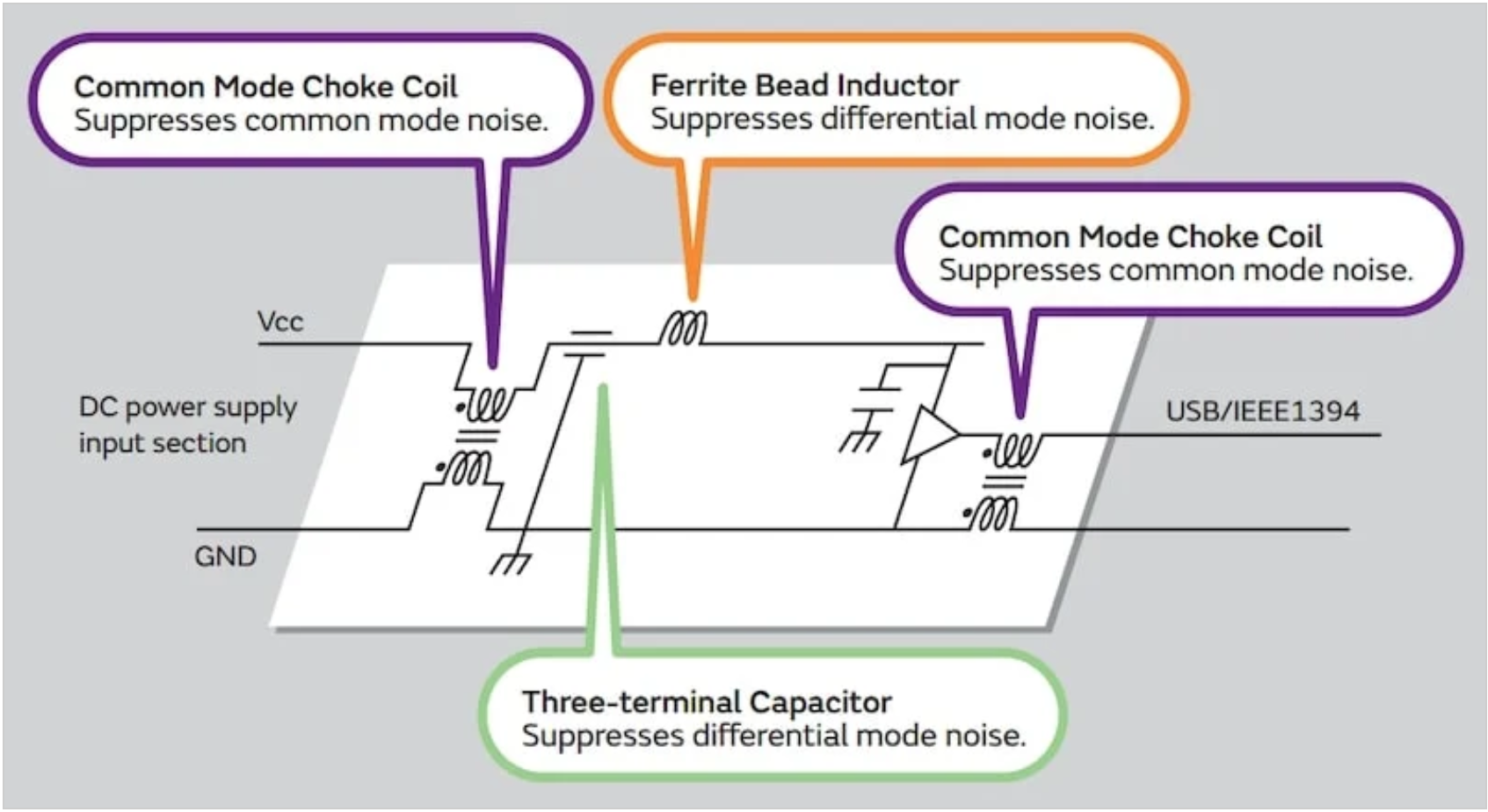

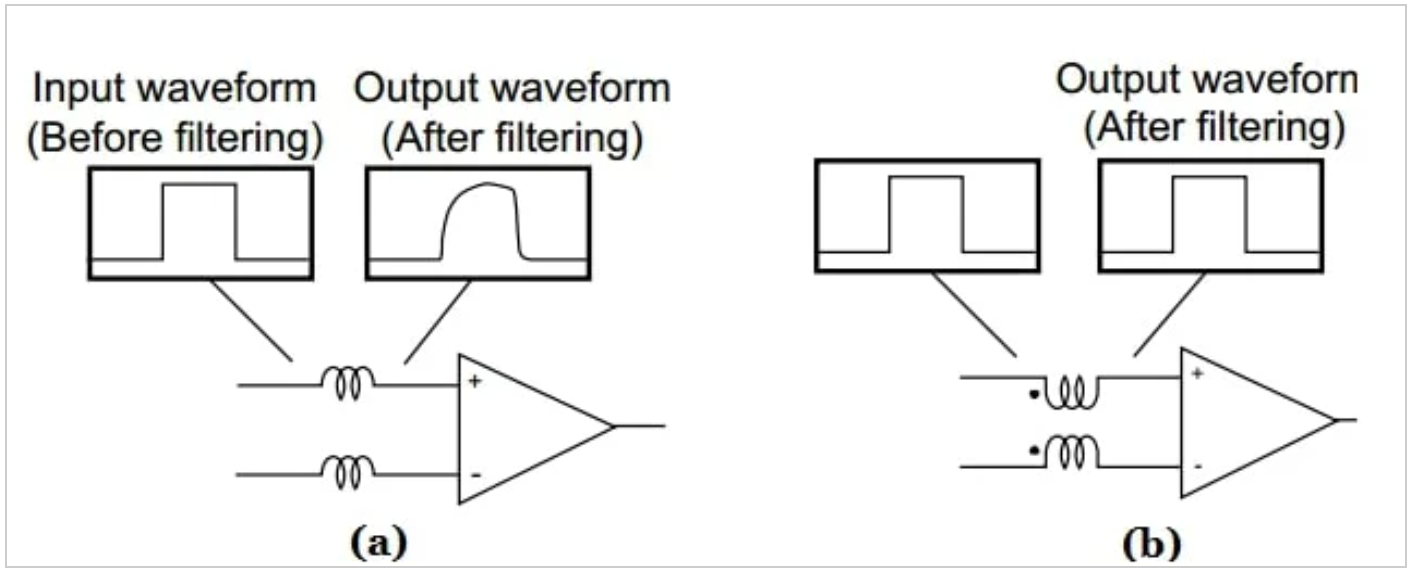

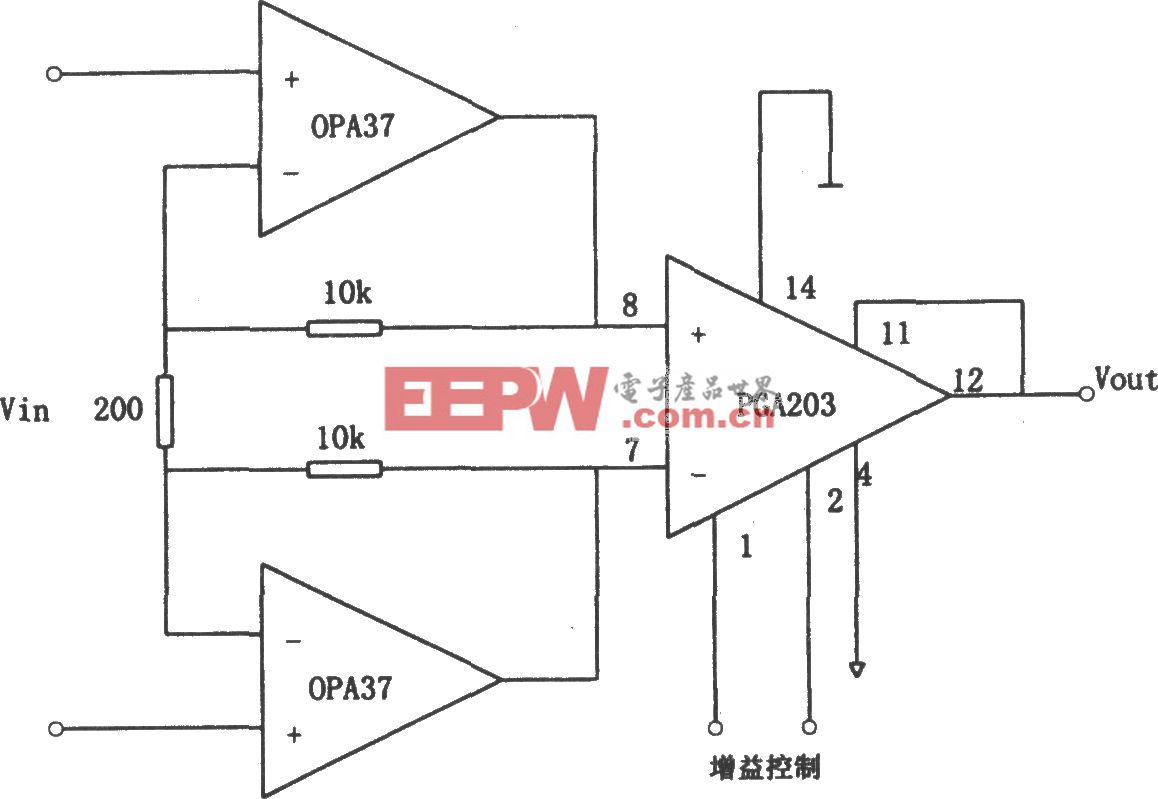

前一篇文章介绍了USB、HDMI和以太网等高速差分数字接口中的共模噪声问题。CMC在这些和其他差分数据传输应用中是有用的。它们还用于过滤开关电源和AC/DC整流器中电源线的噪声。图1显示了CMC的两种不同应用程序。

CMC在电力线和信号线滤波中的应用。

图1。CMC在电力线和信号线滤波中的应用。图片由Murata提供

CMC是如何工作的?

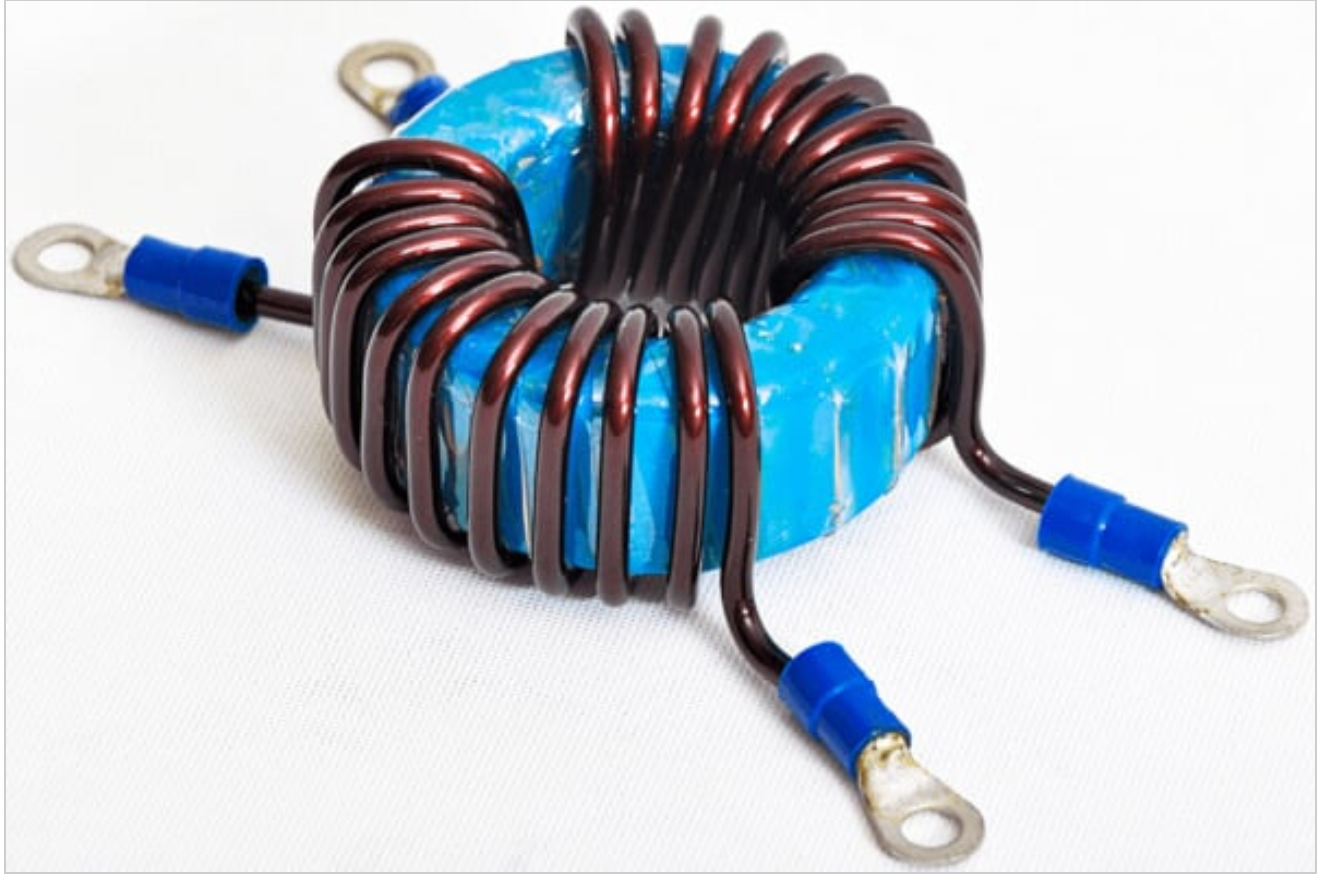

共模扼流圈由缠绕在磁芯上的两个绕组组成。图2显示了用于电源线过滤应用程序的CMC。

用于电源应用程序的CMC。

图2:用于电源应用程序的CMC。图片由Octopart提供

绕组相对于彼此的方向在CMC的操作中起着关键作用。选择它们是为了使设备对共模信号呈现高阻抗,同时使差分信号基本上不受影响地通过。

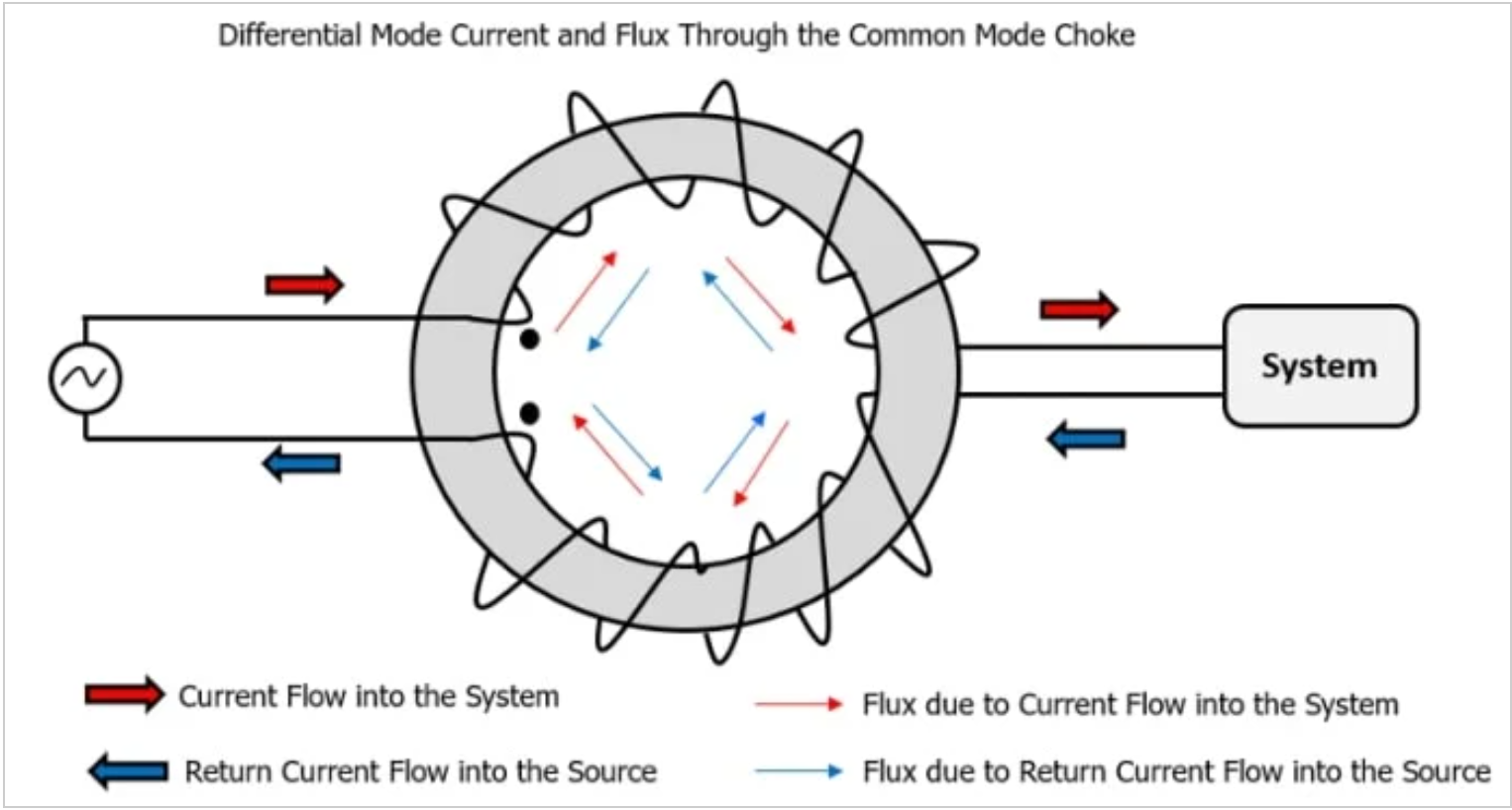

我们可以通过法拉第定律和右手规则来理解CMC的运作。考虑图3中的电流,图3显示了施加差分信号时的CMC。

CMC由差分信号激发。

图3。CMC由差分信号激发。图片由Pulse Electronics提供

利用差分信号,两个绕组产生大小相等但方向相反的磁通量。由于磁通量相互抵消,滤波器对信号的影响应该可以忽略不计,使其能够以最小的衰减通过。由于这种通量消除,差分信号不能驱动CMC的核心达到饱和。

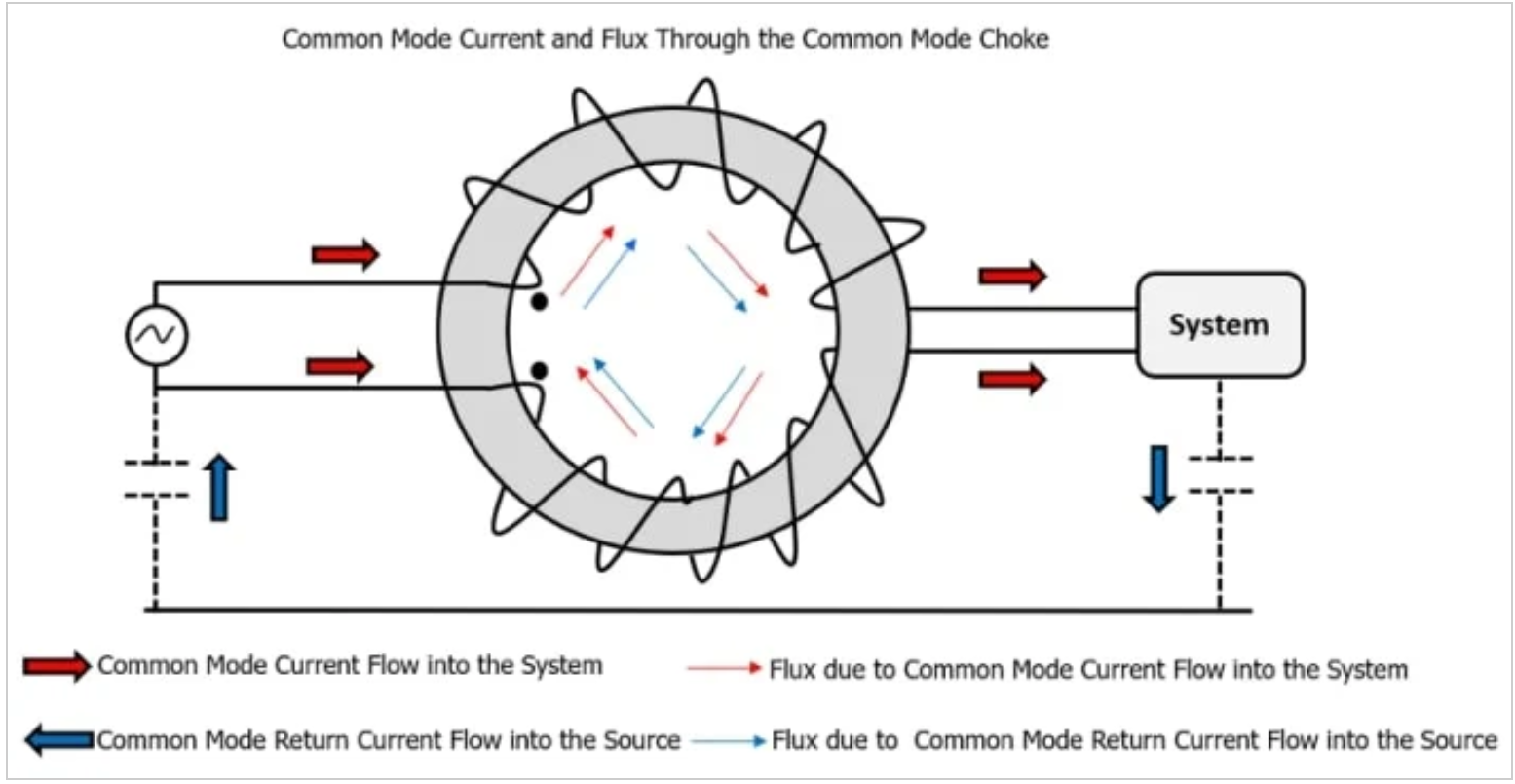

图4显示CMC如何响应共模信号。

CMC由共模信号激励。

图4。CMC由共模信号激励。图片由Pulse Electronics提供

对于共模信号,来自两个绕组的磁通量在同一方向,产生大的电感阻抗。通过呈现高阻抗,该器件有效地抑制了线路中的高频共模噪声。

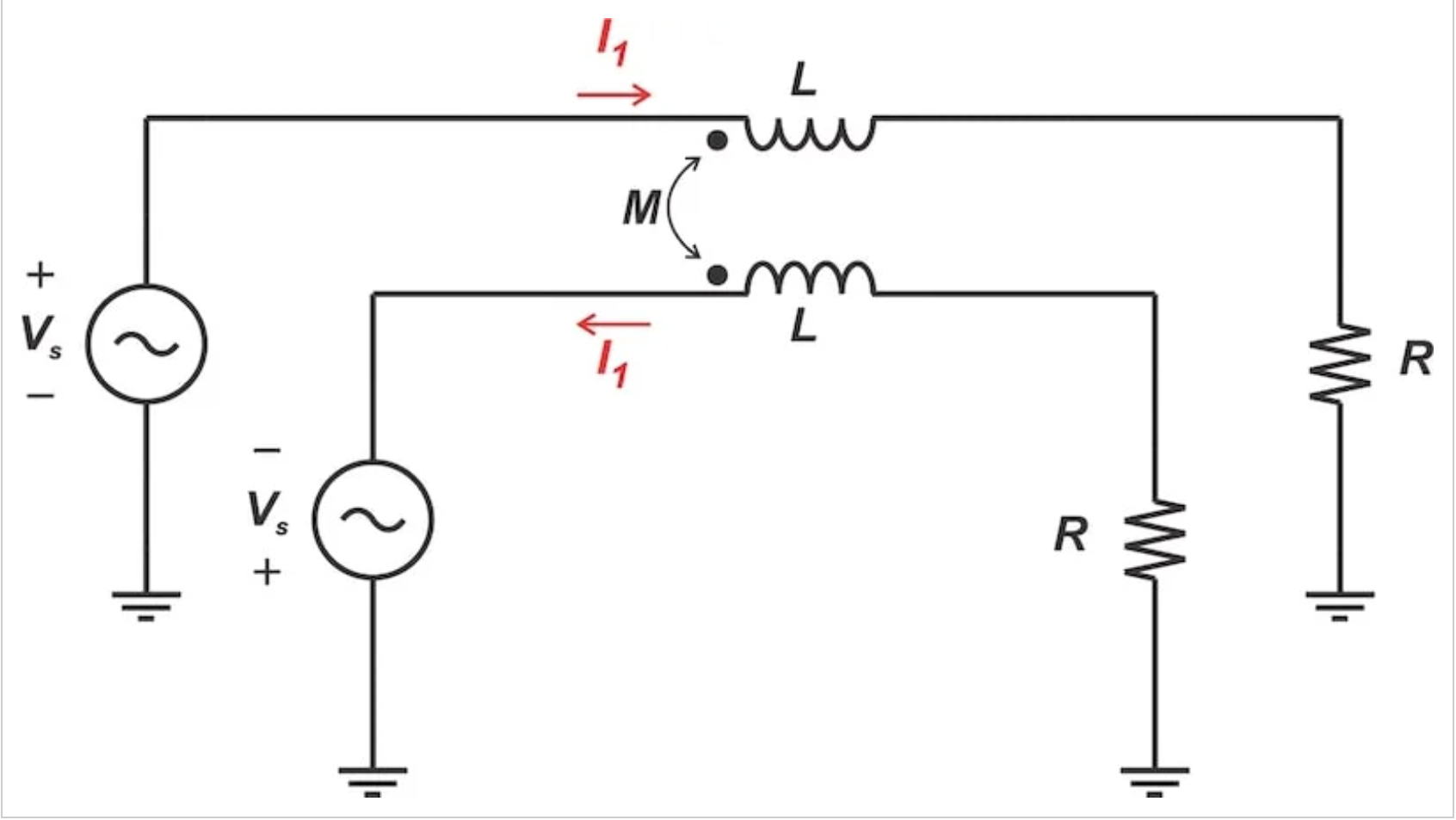

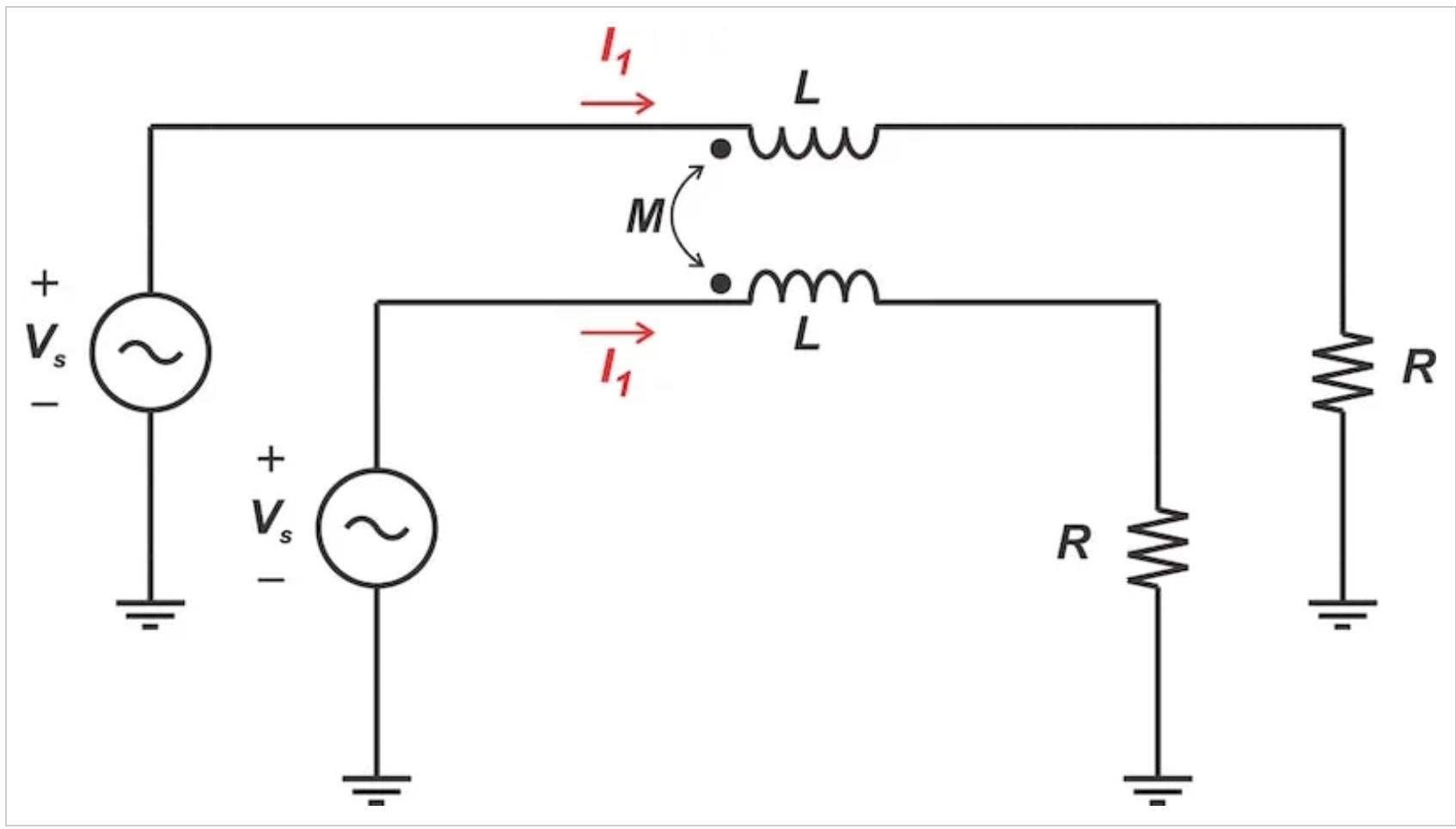

计算差模和共模阻抗

为了量化上述定性描述,让我们计算CMC的差模阻抗和共模阻抗。图5由两个耦合的电感器组成,代表了我们可以使用的最简单的电路模型。对于差分阻抗计算,我们应用差分信号并将输出连接到地。

CMC的一个简单电路模型,用于计算差分阻抗。

图5。CMC的一个简单电路模型,用于计算差分阻抗。图片由Steve Arar提供

在上述模型中,R表示绕组的铜损耗。每个绕组的阻抗为:

等式1。

其中假设绕组之间存在最大耦合(L1=L2=M)。这意味着滤波器理想地对差分信号呈现小的电阻阻抗。正如我们稍后将在文章中讨论的那样,该阻抗应尽可能低。

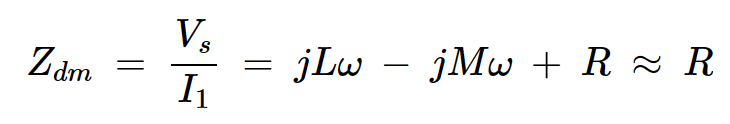

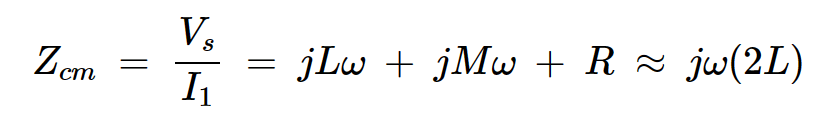

图6对同一电路中的共模激励进行了建模。

CMC的简化模型,用于计算共模阻抗。

图6。CMC的简化模型,用于计算共模阻抗。图片由Steve Arar提供

在这种情况下,每个绕组的阻抗为:

等式2。

其中L⍵õR。共模输入阻抗因此非常高,尤其是在两个绕组之间存在强耦合的频率下。如果CMC使用磁芯,那么在较低的频率下,耦合——以及共模阻抗——将更高,而磁芯在提高电感方面更有效。

如果我们使用两个未耦合的电感器会怎样?

尽管我们可以使用非耦合电感器来抑制差模和共模噪声,但CMC比单独的电感器具有一些重要的优势。例如,由于差模激励期间的磁通抵消,CMC的核心在正常操作期间不会饱和。即使当相对较大的电流流过电路时也是如此。因此,在具有大电流的线路(如AC/DC电源线)上使用CMC来抑制噪声更容易。

在高速数字接口中,CMC对差分信号不可见这一事实也代表了一个优势。图7说明了使用非耦合和耦合电感器来过滤差分信号中的噪声之间的区别。

使用去耦电感器(A)和耦合电感器的滤波前后的差分信号(b)

图7。用去耦电感器(A)和CMC(b)滤波前后的差分信号。图片由Murata提供

在图7(a)中,使用了两个独立的电感器。滤波效果会平滑边缘并使信号失真。上升时间的这种增加可能对信号完整性有害,并导致符号间干扰。相比之下,图7(b)所示的理想CMC根本不会减缓边缘的速度。

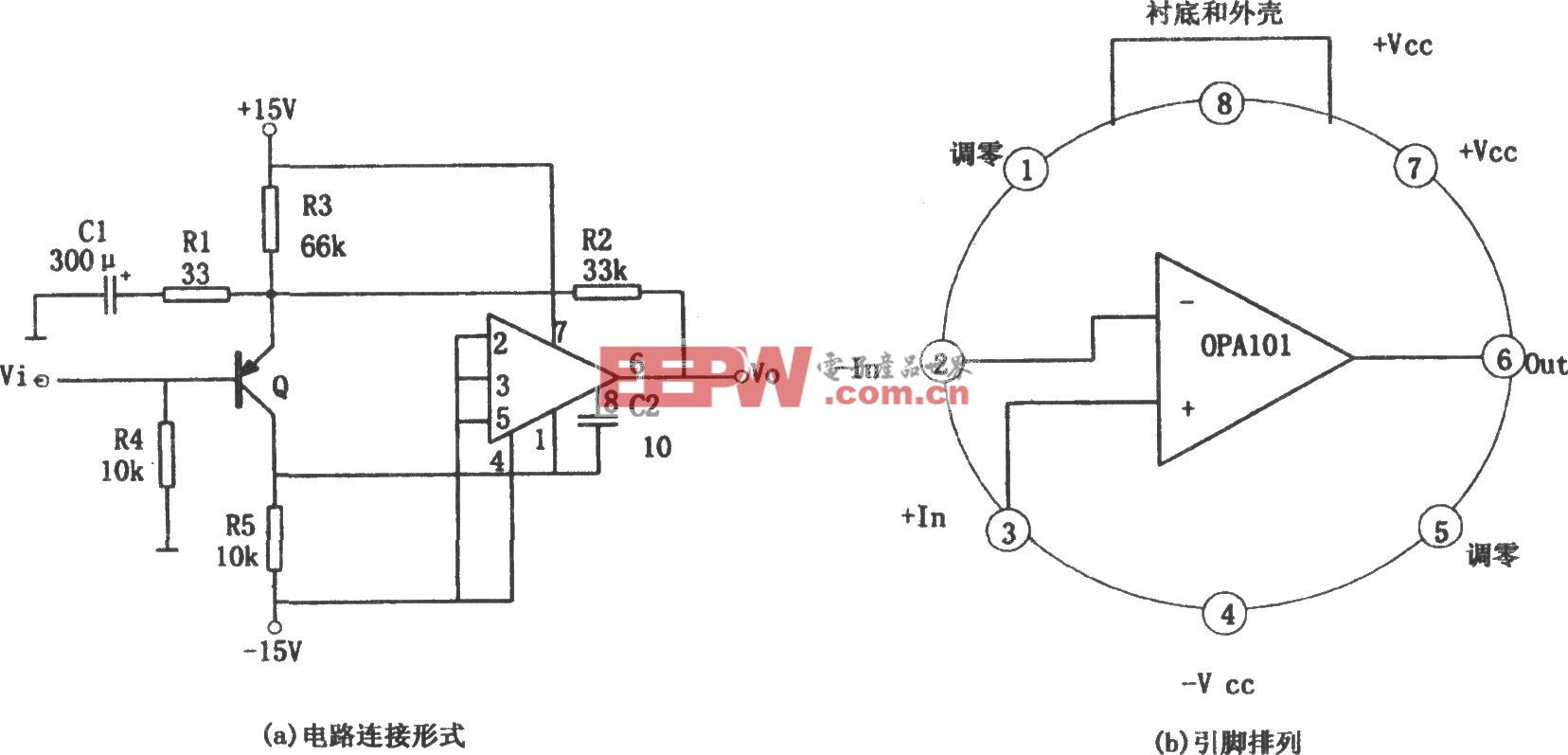

阻抗随频率的变化

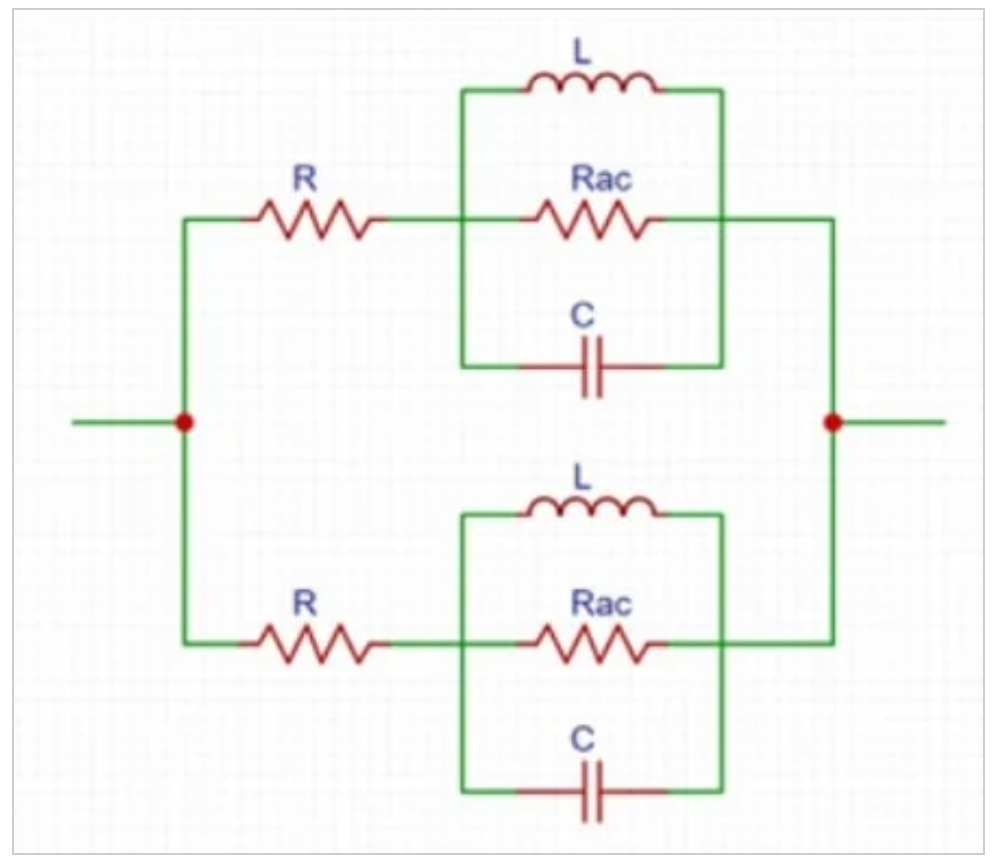

在图5和图6中,我们使用两个耦合电感器对CMC进行建模。这种简化的电路模型忽略了绕组的寄生电容。通过考虑绕组内电容,我们获得了图8中更详细的模型。

共模激励CMC的等效电路模型。

图8。共模激励CMC的等效电路模型。图片由Abracon提供

绕组电容在CMC的频率响应中起着关键作用。在等效模型的核心有一个并联RLC电路意味着有一个谐振频率,并联LC电路的行为就像开路一样。在该频率下,并联RLC电路的阻抗处于其最大值并且等于Rac。

在谐振频率以下,电路表现为电感性的。然而,当我们移动到谐振频率以上的频率时,电路的行为变成电容性的。图9显示了脉冲电子公司的几种不同CMC的阻抗如何随频率变化。

几种CMC的共模阻抗。

图9。几种CMC的共模阻抗。图片由Pulse Electronics提供

如果制造商没有提供CMC的模型,我们可以使用实验室测量来估计图8中模型的参数。该模型可用于模拟CMC对共模噪声的影响。

选择共模扼流圈

在选择共模扼流圈时,我们应该同时考虑其共模阻抗和差模阻抗。差分阻抗应尽可能低,以便所需信号可以不受影响地通过。然而,滤波器抑制噪声的能力直接取决于其共模阻抗——共模阻抗越高,噪声抑制越好。

我们还需要考虑共模阻抗如何随频率变化,以确保它在感兴趣的频率范围内是可接受的高。请注意,较高的共模阻抗通常对应于较大的部件尺寸,这可能更难适应密集的PCB设计。

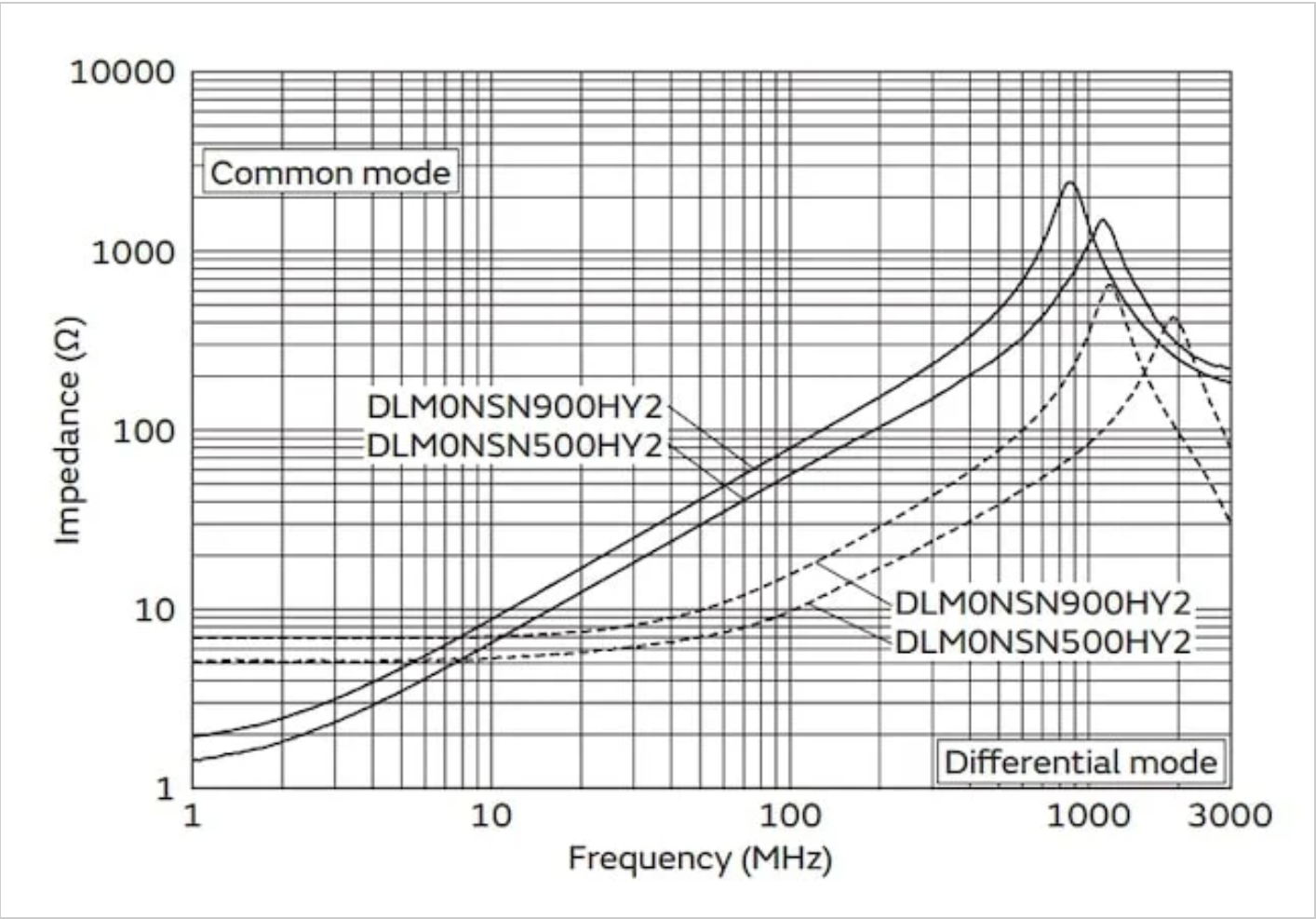

图10显示了Murata的两个CMC的差模和共模阻抗。

CMC数据表中的差分和共模阻抗与频率的关系图。

图10。CMC数据表提供了差分和共模阻抗与频率的关系。图片由Murata提供

在上图中,DLMNSN900HY2的共模阻抗在900MHz左右大于2kΩ。其在相同频率下的差分阻抗约为200Ω。DLM0NSN500HY2的共模阻抗在大约1000 MHz时峰值高于1 kΩ,其中其差分阻抗仅为大约100Ω。

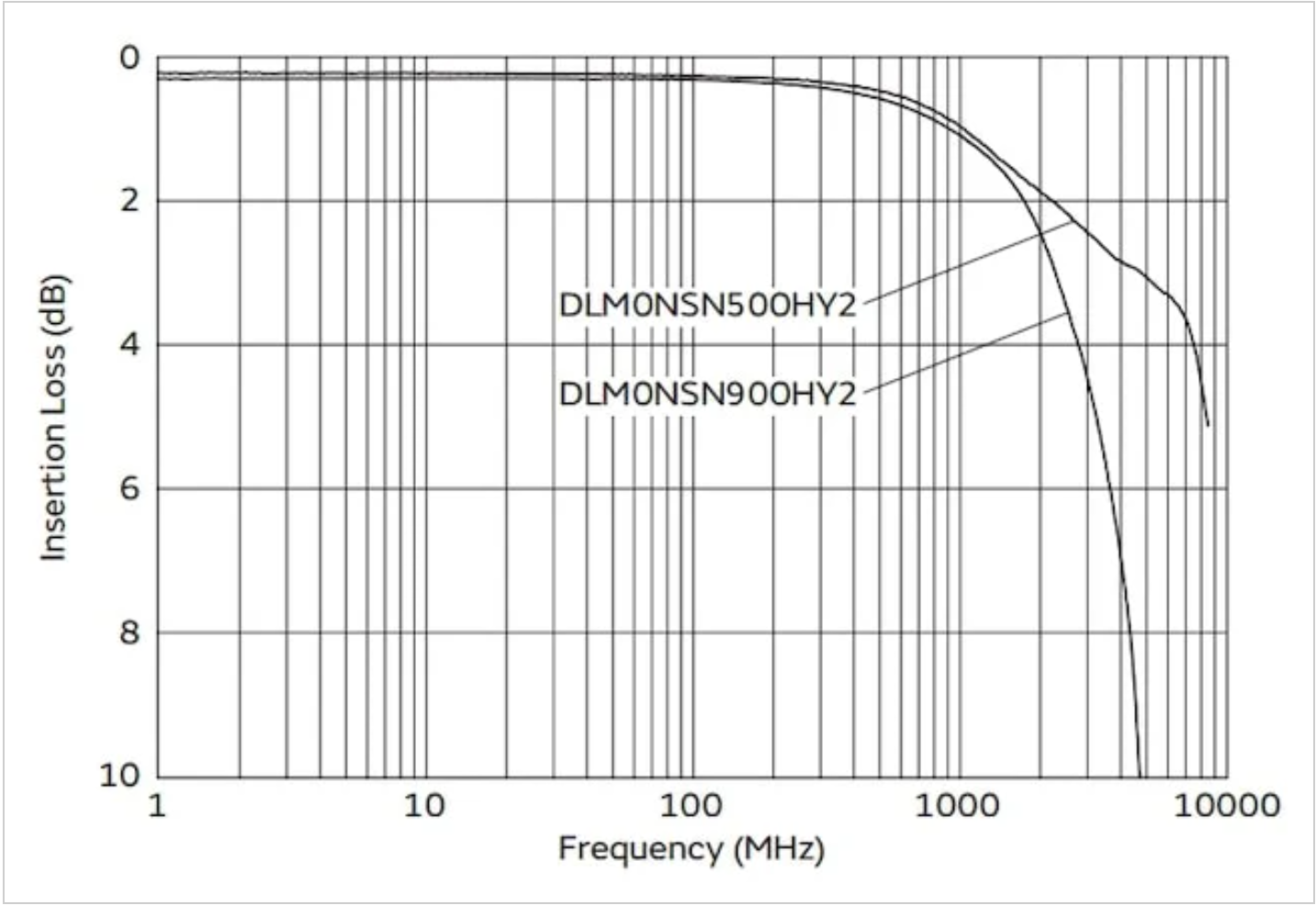

一些数据表还绘制了跨频率的差模插入损耗。上述Murata装置的插入损耗曲线如图11所示。

Murata的两个CMC的插入损耗。

图11。Murata的两个CMC的插入损耗。图片由Murata提供

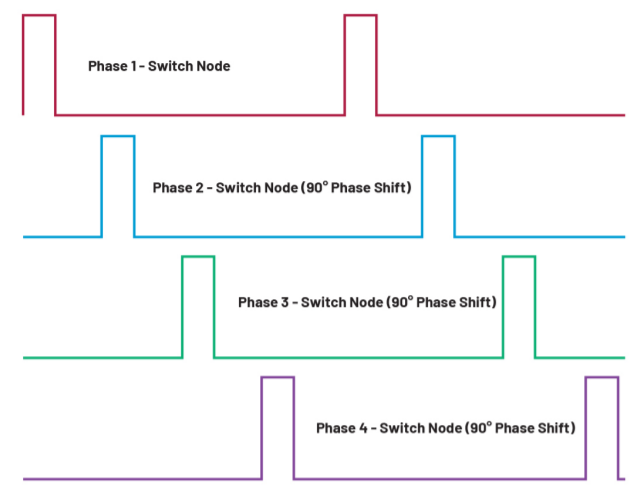

两种不同的缠绕方式:双股和分段

CMC可以使用双线绕组或分段绕组。两者如图12所示。

CMC中使用的双绕组和分段绕组。

图12。CMC中使用的双(左)和分段(右)绕组。图片由Würth Elektronik提供

由于它们具有较低的漏电感,并且对差分信号表现出较小的衰减,双线绕制组件通常用于高速差分信号应用。分段缠绕CMC在绕组之间具有更大的间隔,使其更适合于高电压。然而,这种分离导致更高的漏电感和更高的差分阻抗。

评论