基于PC/104总线的雷达数据采集板设计

摘要:介绍了一种基于PC/104总线的雷达数据采集板的设计。硬件上采用CPLD进行逻辑控制,简化了硬件电路。该采集板具有精度高、成本低等优点,为雷达测试设备的数据采集提供了一套可行的硬件设计方案。

本文引用地址://m.amcfsurvey.com/article/132644.htm引言

随着现代雷达功能多样化、复杂化,要求研制和装备的周期越来越短,为保障装备部队的雷达系统充分发挥出优越的性能,雷达测试设备的作用显得非常重要。本文提出了一种适用于雷达测试设备的数据采集板设计方案,能够有效地对I/Q模拟基带信号进行数据采集和处理,并能满足雷达测试设备小型化的要求。

数据采集板组成及设计原理

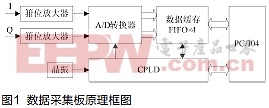

数据采集板由A/D转换电路、数据FIFO缓存电路、CPLD、PC/104CPU模块等四部分组成,其原理框图如图1所示。

A/D转换电路

在本设计中,A/D转换器选用ADI公司生产的12位高速模数转换器AD10242。它是一种全双工、带有模拟输入信号调节的A/D转换器,集成了放大器、基准电压源、模数转换器和输出缓冲器,其采样速率可达40MSPS,采样延迟为1ns。由于雷达模拟基带信号电压变化范围较宽,而AD10242的输入电压只有三档可调:±0.5V、±1.0V、±2.0V,因此为了减小转换误差,使模拟信号在A/D转换器输入的允许范围内尽可能大,就需要对模拟信号的幅值进行必要的调整,即在信号进行模数转换之前对信号进行滤波和降压等信号调理,使其电压符合A/D转换器的要求。本设计中,I/Q模拟基带信号通过2片ADI公司的箝位放大器AD8036,使其信号电压箝位在±1.0V以内。

数据FIFO缓存电路

I/Q模拟基带信号经A/D转换后变为2路12位数字信号,分别连接至2片IDT7203的输入数据总线上。IDT7203是IDT公司生产的高性能FIFO芯片,该芯片是一个双端口的存储缓冲芯片,具有2k×9位的RAM阵列,结构简单,易于操作,其内部的读、写指针可在先入先出的基础上对数据自动写入和读出。IDT7203通过外部电路提供的写信号WR和读信号RD进行数据的读写操作,并提供了三种标志位:全满标志位FF、半满标志位XO/HF和全空标志位EF来标明数据的写入情况,以防止数据的空读和溢出。在本数据采集板中,4片FIFO缓存器均工作在单一器件模式下,用来存储I路和Q路模拟基带信号从启动A/D转换到PC/104总线读取数据的时间内经A/D所转换的数据。在实际使用时,可以通过PC/104软件编程设定FIFO的使用深度,这样可以大大减少A/D转换的中断次数,保证较高的采样频率和较低的中断频率。

评论