满足28 nm迫切的低功耗需求

理想的低功耗元器件

本文引用地址://m.amcfsurvey.com/article/136059.htm制定了这些低功耗目标后,产品开发人员必须进一步提高产品性能,同时降低能耗。而且,降低功耗还有助于帮助最终用户提高经济收益。例如,对于服务供应商依靠电子产品作为其商业模型的情况,降低功耗可以减少与电子设备供电和散热相关的运营开支。而且,降低总功耗能够降低实际供电需求。所有这些因素都有利于减小设备规模,降低投入和运营成本。如通过供应链来降低功耗需求所示,这些最终用户需求转换为设备供应商的需求,最终是元器件供应商的需求。

FPGA和可编程逻辑器件(PLD)非常适合产品开发人员通过以下方式,以低成本来控制功耗:

- 将大量的板上逻辑、存储器和处理器元件迅速集成到很少的器件中,甚至是一个器件中。

- 减少支持元件和供电电源数量,减小电路板面积,降低实现复杂电子系统所需要的功耗。

- 支持采用不同的实现方法和算法来精确的调整功耗。

灵活的可编程逻辑具有低功耗优势,在综合考虑全定制硅片的成本和产品及时面市时,它是非常有吸引力的选择。

在28 nm定制功耗

在28-nm节点,设计人员利用Altera器件可以针对特定的目标市场和应用来定制功耗。Altera的方法在28-nm系列产品中利用了多种半导体工艺,针对产品和某些系列体系结构进行了优化,增强了IP。结果,与前一代同类产品相比,Altera的28 nmFPGA功耗降低了40%。

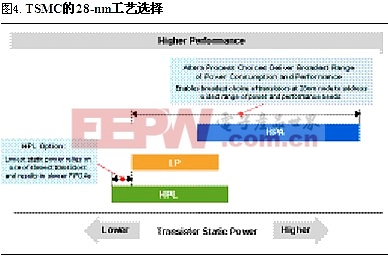

TSMC的28-nm工艺选择 显示了台积电(TSMC)的三种28-nm工艺技术,该公司是可编程逻辑供应商的28-nm节点半导体代工线。在这些工艺中,大量晶体管具有较大的静态功耗范围。左侧的晶体管静态功耗较低,而右侧的较大。这也体现了静态功耗与这些晶体管性能之间的关系。总体上,晶体管性能越好,静态功耗也就越高。Altera在28 nm产品上同时使用了28LP和28HP工艺来提高性能范围,以及多种功耗选择。第三种工艺选择是28HPL,某些晶体管的静态功耗较低,位于标以“HPL Option”的部分中,但是大量使用这类晶体管会导致FPGA运行较慢,对于很多设计人员而言是无法接受的。相应的,FPGA的28HPL工艺需要使用高速低泄漏晶体管,无法体现静态功耗的优势。

在28-nm节点,Altera器件是所有FPGA中总功耗最低的。这些器件之所以具有优异的功耗特性,是因为在产品开发的所有阶段都非常注重降低功耗。从28HP和28LP半导体工艺就开始重视降低功耗。

f 关于Altera注重降低高性能28HP Stratix®V器件系列功耗的详细信息,请参考“降低28-nm FPGA功耗,提高带宽”白皮书。

与Stratix V系列不同,Altera的其他28-nm FPGA产品——Cyclone®V和Arria®V系列,设计用于不需要绝对最高性能和带宽的应用。结果,它们基于28LP工艺,设计用于提供最低总功耗,如TSMC所述:

“与TSMC的40LP技术相比,基于SiON的28LP工艺采用了该系列中最低总功耗和高性价比技术,其逻辑密度将翻倍,速度提高50%,功耗降低30-50%。”

评论