满足28 nm迫切的低功耗需求

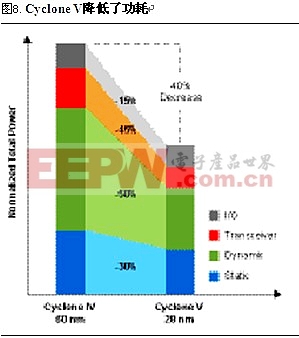

通过这些静态和动态功耗优化措施,Altera基于28LP的FPGA总功耗比前几代器件降低了40%,全面降低了功耗,如Cyclone V降低了功耗所示。

本文引用地址://m.amcfsurvey.com/article/136059.htm

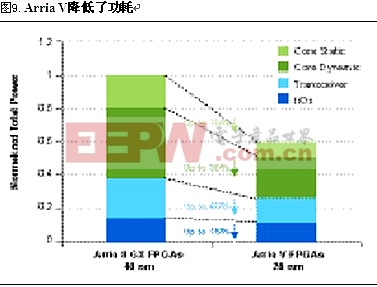

显示了Arria V器件相似的结果。

通过软件创新降低功耗

在工艺和体系结构创新基础上,Altera在Quartus II的软件功耗优化方面进行了大量的投入。功耗驱动的编译使用功耗驱动综合和功耗驱动布局布线功能,主要用于降低设计的总功耗。对于设计人员而言,这种功耗驱动的方法是透明的,通过简单编译设置来实现。设计工程师将时序约束简单地设置为设计输入过程的一部分,对设计进行综合,满足性能要求。Quartus II为每一功能模块自动选择所需的性能,并通过功耗预知布局布线和时钟技术来降低功耗,如包括自动功耗优化的Quartus II设计流程所示。

评论