基于TSI578的串行RapidIO交换模块设计

1.3 时钟设计

TSI578芯片需要3个时钟源,其中一路156.25MHz差分对时钟输入(S_CLK_p/n)用来控制信号的传输速率,另一路100 MHz共模时钟信号(P_CLK)用以控制TSI578内部寄存器的访问。另外,由100 MHz的高稳晶振产生的时钟信号经过驱动芯片后,其中一路可提供P_CLK时钟,另外一路经过AD9516芯片产生所需的差分时钟信号S_CLK_p/n。RapidIO数据的传输波特率可通过管脚,分别设置为1.25G、2.5G和3.125G。

1.4 复位设计

外部复位信号在输入后,可与手动复位信号一起作为逻辑门的输入,逻辑门的输出连接至FPGA的复位控制管脚,从FPGA产生的复位信号可直接提供给TSI578以及其它芯片作为复位输入。

2基于信号完整性的高速电路板设计

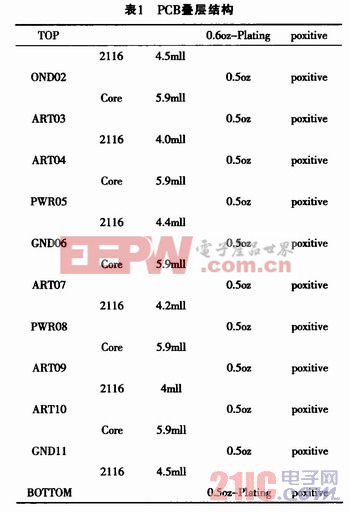

对于高速电路板来说,信号完整性问题是非常关键的一个问题。信号完整性设计包括两个方面,一个是原理图中的信号完整性设计,另一个是PCB中的信号完整性设计。在原理图设计中,主要考虑反射和地弹效应。对于以上两个效应的处理,可分别采用阻抗匹配和去耦电容两种方法进行处理。为了更好的解决信号完整性问题,通常只局限于原理图设计是远远不够的,更多的工作还在PCB的设计中。PCB中的信号完整性分析包括布线前仿真和布线后仿真,前仿真是指在PCB布局、布线之前,对原理图中的高速信号进行仿真,以考察信号在虚拟的叠层结构与布线参数下的传输效果,帮助设计者优化出一套适合当前电路的PCB叠层结构、布线阻抗与高速设计规则(线宽、线长、间距等)。后仿真则提供批处理仿真功能,它对PCB进行整板或关键网络进行交互式仿真分析,输出精确的信号波形、电磁辐射频谱或眼图,设计者可以修改布线参数后再仿真,从而发现并改善不合理的布线。本设计中的SRIO信号是关键的高速信号,根据PCB仿真结果设计出的PCB叠层结构和设计规则如表1和表2所列。本文引用地址://m.amcfsurvey.com/article/156523.htm

评论