FreeARM7 IP核的微处理器逻辑扩展与验证

摘要:介绍了FreeARM7 IP核的基本概况及其接口特点,以LPC2101为原型对该IP核进行了扩展。结合USB 1.1设备控制器IP核和自定制硬件逻辑,构建了一种微控制器功能验证回路。在主机端开发了验证程序、驱动和通信软件。验证程序下栽执行结果表明,功能验证回路工作正常,微处理器运行稳定。

关键词:FteeARM7;LPC2101;微处理器;USB

1 FreeARM7 IP核简介

FreeARM微处理器的ARM7系列(简称FreeARM7)首发于www.socvista.com,由Free-arm联合其他ARM爱好者基于ARMv4架构开发而成。整个

IP核代码采用可综合的Verilog HDL描述,接口简单,描述精炼,全部代码不超过2000行。在整体设计上,采用了三级流水线和哈佛结构,全面兼容各种中断和操作指令(除Thumb和协处理器指令)。经过评估可知,该IP核基于FPGA和SMIC工艺库都有很好的实现结果。

FreeARM7接口定义如表1所列,概括起来可分为4类:

◆系统接口,提供系统控制信号;

◆中断源,提供ARM架构需要的5个中断信号;

◆ROM接口,与提供指令的ROM之间的接口;

◆单口RAM接口,与单口RAM和外设之间数据交互的接口。

其中,单口RAM接口可以实现两类用途:一、挂接单口RAM,使得FreeARM7能够正确地读写数据;二、挂接外设,使得FteeARM7能够正确操作外设。

2 微处理器改进与逻辑扩展

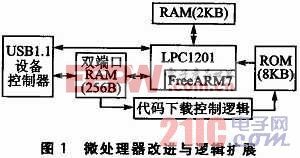

基于FreeARM7的微处理器改进与逻辑扩展的结构如图1所示。预期的实现目标是:在主机上编写嵌入式程序汇编成机器码后,经过USB 1.1设备控制器传输至双端口RAM中,在微处理器代码下载模式下,代码下载控制逻辑将双端口RAM中的机器代码装载至ROM中,之后启动微处理器正常工作模式,微处理器执行ROM中的嵌入式代码,接收主机通过USB传送来的参数值,并将运行结果通过USB返回至主机。

基于Cyclone II FPGA具体实现时,ROM、RAM和双端口RAM都是利用Quartus II软件中MegaWizardPlug-In.Manager工具例化相应的存储模块,而其他硬件逻辑的扩展都是以IP核(Verilog描述)的形式出现。

评论