数字控制挑战传统电源设计理念VMC、CMC

电源设计之初所要求的基本决定之一是:采用电压模式控制(VMC)还是采用电流模式控制(CMC)。对任何设计而言,交易存在于两个执行方法之间。然而,由于数字控制方法的引入,这些已被尝试并值得信赖的交易正面临着严峻挑战。本文将研究这条绘制的主线,以及数字控制是如何在是否采用VMC还是采用CMC的交锋中成为一种不可阻挡的再认知的。

本文引用地址://m.amcfsurvey.com/article/180182.htm方法

大量详实的材料充分的描述了电流模式控制和电压模式控制,因此本文只作一下简单的回顾。VMC由单个控制环路组成,该环路采用输出电压作为反馈信号。输出电压改变之后环路重新动作产生一个瞬时响应去替换。由于我们的目标是要维持一个恒定输出电压,因此缓慢响应是一个明显的缺陷。CMC添加了一个外部反馈环路。除电压控制环路外,它还对电流流向敏感以及对峰值电流到达时电源开关的关断动作敏感。电流信号作为主要的控制环路。也许有人会认为VMC和CMC比较会有更缓慢的响应,但这种观点是不正确的,因为环路响应最终是由系统带宽决定的。两种方法都可以设计出相同的环路带宽,因此VMC并不一定必然比CMC慢。

克服VMC问题

由此,让我们研究一下传统观念,即为何VMC或CMC会成为首选方案。在推挽或全桥式电路拓扑中,流向开关电路两个管脚的电流也许并不总是相等。这将会导致FET失衡或定时错误。其网络影响是会在变压器上产生直流建立,这将会迅速的导致变压器核饱和。传统的方法是采用一个电容和主变压器串联起来。

该直流阻塞电容可耦合交流信号,这样可以阻止变压器核的饱和。这样做的缺点是要和主电源路径串联,因此它必定是一个可靠器件。要求可供1kW电源使用、10uF等级的阻塞电容的额定值必定要超过全电压波动。而且,变压器通常都要采用冗余设计来抑制饱和。由于CMC的控制环路在超过两个管脚相同电流极限时关断了电源开关,因此CMC并不会因此表象受损。这意味着变压器中没有直流电流建立。

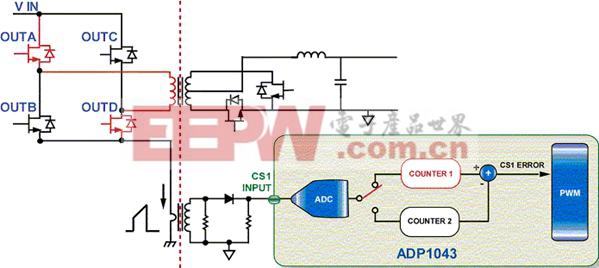

图1描述了数字控制是如何解决这个问题的。控制器测量每个半桥电路的电流并计算其差值。差值信号驱动主PWM信号对失衡进行补偿。从概念上来说,此方法和CMC是相似的,这可以视为平均CMC而不是峰值CMC。

图1:带有集成电压次级平衡电路的数字控制器。

环路稳定性和滤波

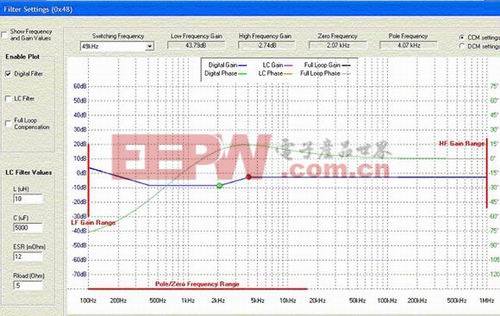

由于CMC环路近似为单极性滚轮(每十年-20°dB)的控制输出传递功能,所以通常认为稳定CMC环路要比稳定VMC环路要容易。VMC环路近似为双极性滚轮(每十年-40°dB)的传递控制,这样使得补偿网络变得更加复杂。在另外一个领域里,数字控制在这场交锋中呈现出了一个全新面貌。用户友好型的图形用户接口(GUI)的出现意味着环路补偿已成为了简单任务。设计者输入所需的滤波器响应,GUI就会计算滤波器实现响应所需的系数。不仅一个良好设计的GUI去掉了外部复杂性,而且也前进了一大步,因为它使得整个补偿程序比以前简单了很多。

图2:滤波器补偿图形用户接口。

评论